## **DESIGN FOR PRE-BOND TESTABILITY IN 3D**

# **INTEGRATED CIRCUITS**

A Dissertation Presented to The Academic Faculty

By

Dean L. Lewis

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology December 15, 2012

Copyright © 2012 by Dean L. Lewis

# DESIGN FOR PRE-BOND TESTABILITY IN 3D INTEGRATED CIRCUITS

Approved by:

Dr. Hsien-Hsin S. Lee, Advisor Associate Professor, School of ECE Georgia Institute of Technology

Dr. Muhannad Bakir Associate Professor, School of ECE Georgia Institute of Technology

Dr. Sung Kyu Lim Associate Professor, School of ECE Georgia Institute of Technology Dr. Richard Vuduc Assistant Professor, College of Computing Georgia Institute of Technology

Dr. Sudhakar Yalamanchili Professor, School of ECE Georgia Institute of Technology

Date Approved: July 27, 2012

To my amazing, wonderful, loving wife Heather.

#### ACKNOWLEDGMENTS

The completion of a dissertation is a long and arduous process, and I never could have done it alone. Here I would like to thank the many, many people who have helped and supported me along the way.

First, my thanks to my adviser, Professor Hsien-Hsin S. Lee for giving me the opportunity to study under him, for assisting and guiding my research, and for ensuring my success as a scientist, engineer, and academic. I also want to thank Professor Sung Kyu Lim and Dr. Gabriel Loh for their guidance and mentorship in the 3D research group.

My thanks to Professor Muhannad Bakir, Professor Richard Vuduc, and Professor Sudhakar Yalamanchili for lending me their time and insight as members of my dissertation committee. My thanks to Professor David Keezer and Professor Linda Milor as well for serving on my proposal committee.

My thanks to the current and former members of the MARS lab for their years of insight, mentoring, and friendship: Dr. Nak Hee Seong, Dr. Richard Yoo, Manoj Athreya, Ali Benquassmi, Andrei Bersatti, Nishank Chandawala, Eric Fontaine, Jen-Cheng Huang, Ilya Khorosh, Tzu-Wei Lin, Mohammad Hossain, Fayez Mohamood, Lifeng Nai, Ahmad Sharif, Guanhao Shen, Vikas Vasisht, and Sungkap Yeo. A special thanks to Dr. Mrinmoy Ghosh and Dr. Dong Hyuk Woo for their friendship and for leading-by-example in their own Ph.D. studies.

My thanks to the current and former members of the GTCAD lab: Krit Athikulwongse, Rohan Goel, Moongon Jung, Young-Joon Lee, Chang Liu, Pratik Marolia, Shreepad Panth, Mohit Pathak, Hemant Sane, and Taigon Song. A special thanks to Dr. Michael Healy, Dr. Dae Hyun Kim, and Xin Zhao for their friendship and their crucial assistance in the development and publication of my research.

My thanks to the members of the 3D-MAPS design team for the unique opportunity to create a working microprocessor with them. In additional to those mentioned above, my

thanks to Gokul Kumar and Minzhen Ren for this special project.

My thanks to the Georgia Tech community and the wonderful environment they have created there. A special thanks to Dr. Tapobrata Bandyopadhyay, Professor Jeff Davis, Dr. Carl Gray, Dr. Chris Lee, Professor Milos Prvulovic, Dr. Samantika Subramaniam, Pam Halverson, Andrew Kerr, Beverly Scheerer, and Jeff Young. A special thanks to my close friends Dr. Demijan Klinc, Dr. Matthew Lynch and wife Lisa, Dr. Ioannis Doudalis, Professor Guru Venkataramani, and Dr. Kiran Puttaswamy for their companionship, insight, banter, and guidance.

My thanks to the global research community, including conference attendees, reviewers, and funding agencies. A special thanks to Dr. Eric Jan Marinissen for his guidance, feedback, and encouragement.

My thanks to the VCU School of Engineering, the Chesterfield County Math and Science Highschool, and the countless friends and mentors I have had along the way. A special thanks to Lee Adcock, Vivek Agarwal, Jake Bono, Jeremy Davis, Lorie Ros Jacob, Jeff McBride, Jason Naggles, Eric Reisinger, Sarah Rigsbee, Kerry Rose, Brandon Saunders, Julie Wald, and Grant Withers. My life would be unrecognizable without them.

My thanks to my family for their undying support. I am especially thankful for my grandparents, Roy and Marie Lewis and Freeland and Norma Young, four wonderful people who made me who I am, and for my brother Geoff for toughening me up along the way. And I cannot even properly describe my love and my appreciation for my parents, Roy and Jane Lewis. None of this would have been possible without their unwavering love, support, guidance, friendship, and encouragement. From them I learned the value of hard work, commitment, and a kind heart, and to them I owe everything.

Finally, my thanks and my heart to Heather, my wife, for her endless love, support, encouragement, and devotion. Heather, I love you!

## TABLE OF CONTENTS

| ACKNO   | WLEDGMENTS                                                |

|---------|-----------------------------------------------------------|

| LIST OF | TABLES                                                    |

| LIST OF | FIGURES                                                   |

| SUMMA   | <b>RY</b> xii                                             |

| СНАРТИ  | <b>ER 1 INTRODUCTION</b>                                  |

| СНАРТЕ  | <b>ER 2</b> ORIGIN AND HISTORY OF THE PROBLEM             |

| 2.1     | Design for Test                                           |

| 2.2     | 3D Integration                                            |

| 2.3     | 3D Testing                                                |

| СНАРТЕ  | <b>ER 3 PRE-BOND TEST ARCHITECTURE AND APPLICATION</b> 11 |

| 3.1     | Requirements                                              |

| 3.2     | Hardware                                                  |

| 3.3     | Experiments                                               |

| 3.4     | 3D-MAPS Test Architecture                                 |

| 3.5     | Summary                                                   |

| СНАРТЕ  | <b>ER 4 3D CIRCUIT DESIGN FOR PRE-BOND TEST</b> 34        |

| 4.1     | 3D Circuit Design and Test                                |

| 4.2     | Experiments                                               |

| 4.3     | Summary                                                   |

| СНАРТЕ  | <b>ER 5 3D TEST WRAPPERS</b> 46                           |

| 5.1     | Problem Definition                                        |

| 5.2     | Wrapper Design Algorithm                                  |

| 5.3     | Experiments                                               |

| 5.4     | Summary                                                   |

| СНАРТЕ  | <b>ER 6 SHORTING PROBE</b>                                |

| 6.1     | 3D Via Defects                                            |

| 6.2     | 3D Via Probing                                            |

| 6.3     | Experimental Setup                                        |

| 6.4     | Results                                                   |

| 6.5     | Physical Considerations                                   |

| 6.6     | Summary                                                   |

| CHAPTER 7 RECENT DEVELOPMENTS | 5 |

|-------------------------------|---|

| 7.1 IEEE P1838 Standard       | 5 |

| 7.2 Pre-bond Test             | 6 |

| 7.3 Post-bond Test            | 7 |

| 7.4 3D Assembly               | 9 |

| 7.5 3D Via Repair             | 0 |

| CHAPTER 8 CONCLUSION          | 2 |

| <b>REFERENCES</b>             | 4 |

# LIST OF TABLES

| Table 1  | List of buses in 3D 21264 layout                    | 18 |

|----------|-----------------------------------------------------|----|

| Table 2  | Global control signals                              | 27 |

| Table 3  | Physical design costs of 3D adder                   | 43 |

| Table 4  | Adder power and performance results                 | 43 |

| Table 5  | Test vectors required for Kogge-Stone adder designs | 44 |

| Table 6  | Two-tier circuit benchmarks                         | 54 |

| Table 7  | Four-tier circuit benchmarks                        | 55 |

| Table 8  | Stitching wire reuse results                        | 59 |

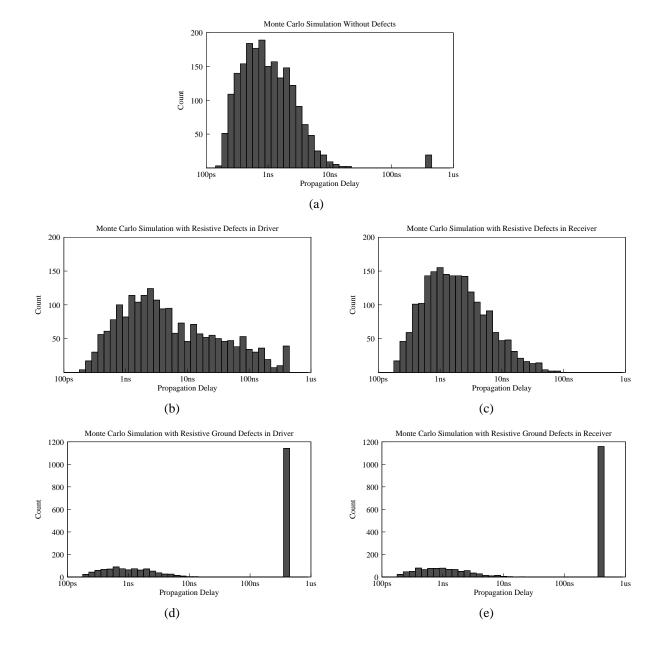

| Table 9  | Shorting probe circuit parameters                   | 75 |

| Table 10 | Sensitivity analysis variables                      | 76 |

| Table 11 | Monte Carlo statistical results                     | 88 |

### LIST OF FIGURES

| Figure 1  | Digital logic operational modes                   | 4  |

|-----------|---------------------------------------------------|----|

| Figure 2  | 3D integrated die stack                           | 7  |

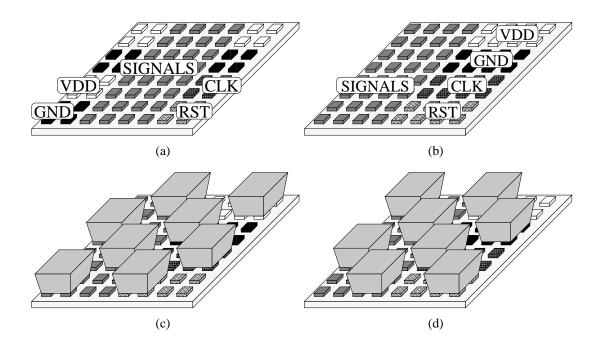

| Figure 3  | 3D architectural partitioning                     | 12 |

| Figure 4  | 3D scan-based test architecture                   | 14 |

| Figure 5  | 3D test-aware clock tree design                   | 15 |

| Figure 6  | 3D test-aware power rail design                   | 16 |

| Figure 7  | Floorplan for 3D 21264 case study                 | 17 |

| Figure 8  | The 3D-MAPS chip stack                            | 19 |

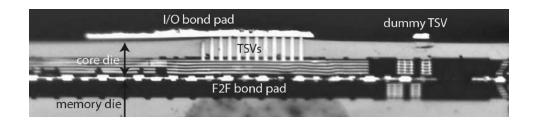

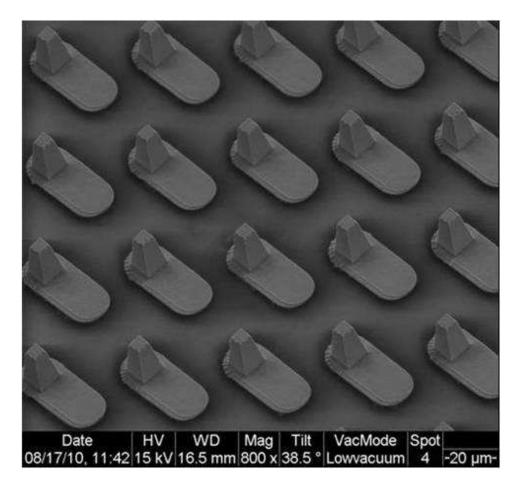

| Figure 9  | SEM image of the 3D-MAPS chip stack               | 20 |

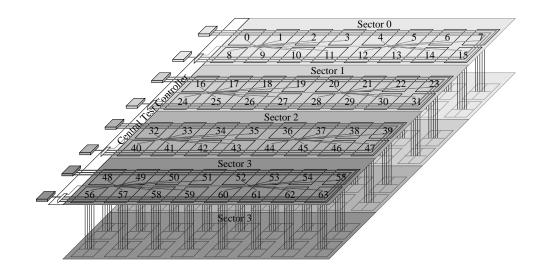

| Figure 10 | Sector test architecture                          | 21 |

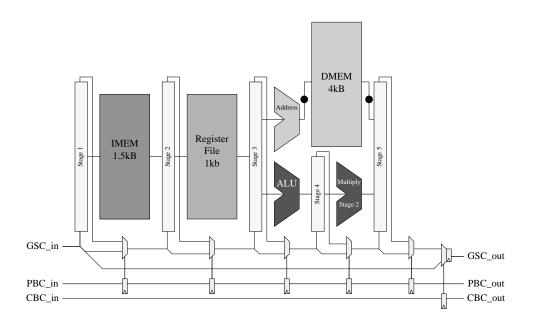

| Figure 11 | 3D-MAPS single core architecture                  | 24 |

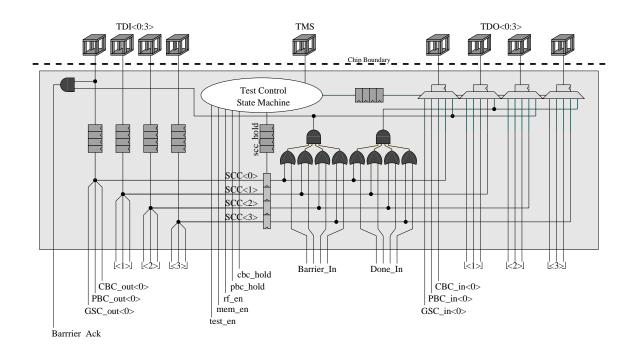

| Figure 12 | CTC circuit diagram                               | 25 |

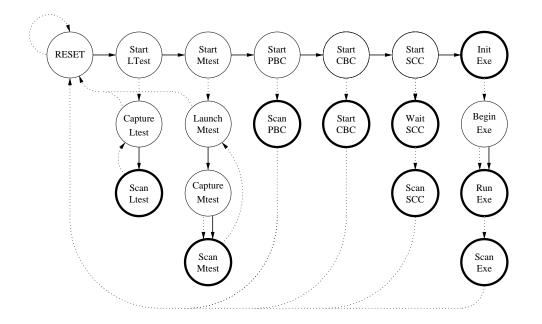

| Figure 13 | TCSM state transition diagram                     | 26 |

| Figure 14 | 3D test path schematic                            | 30 |

| Figure 15 | Screen capture of a 3D-MAPS test vector           | 31 |

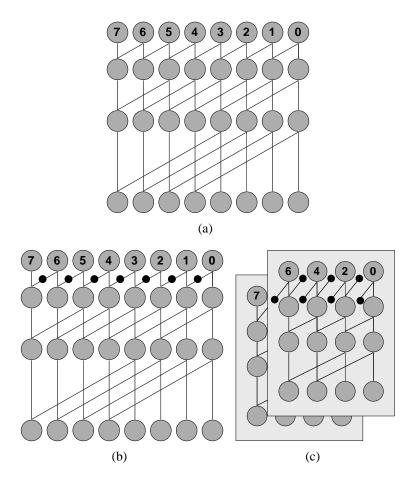

| Figure 16 | Kogge-Stone adder schematics                      | 35 |

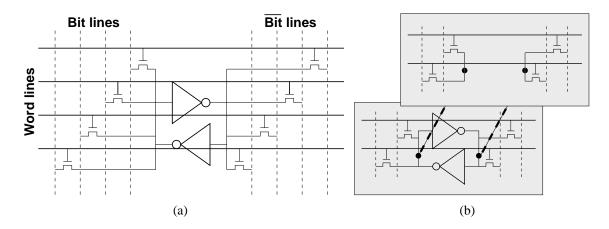

| Figure 17 | Register file schematics                          | 37 |

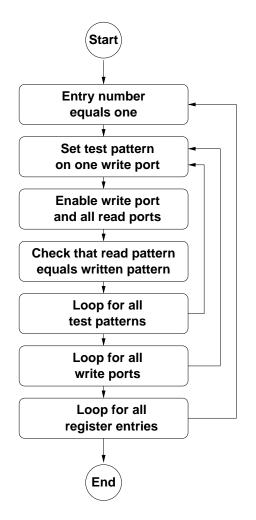

| Figure 18 | Flowchart of the 3D register file test algorithm  | 39 |

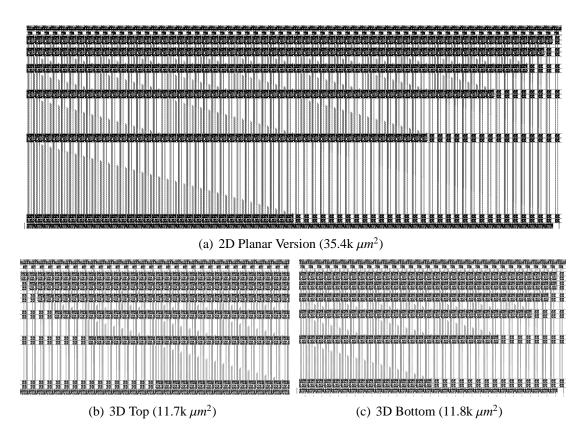

| Figure 19 | Layouts for a 64-bit Kogge-Stone Adder            | 40 |

| Figure 20 | Layouts for a 1kb register file                   | 41 |

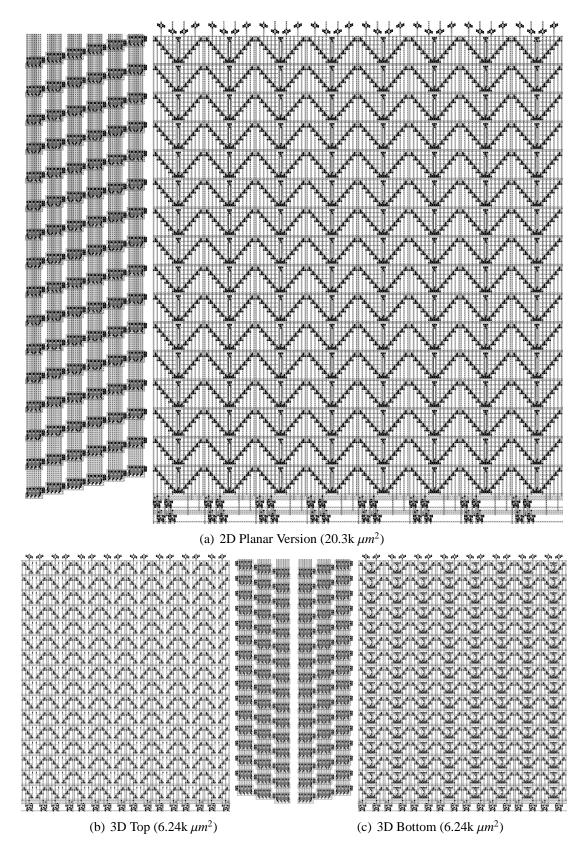

| Figure 21 | Motivation for the 3D wrapper design problem      | 48 |

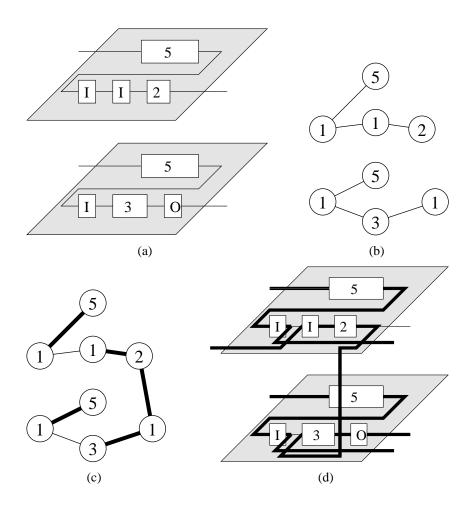

| Figure 22 | Visual description of 3D wrapper design algorithm | 50 |

| Figure 23 | Psuedo-code description of KL algorithm           | 52 |

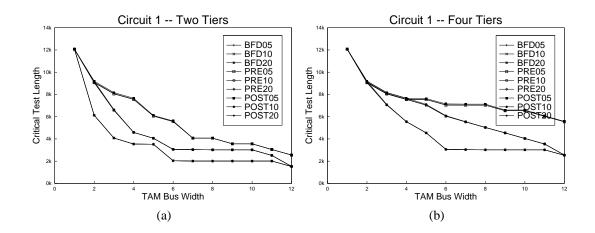

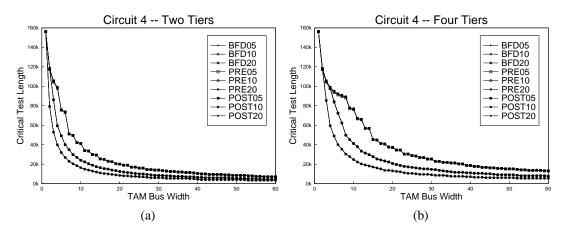

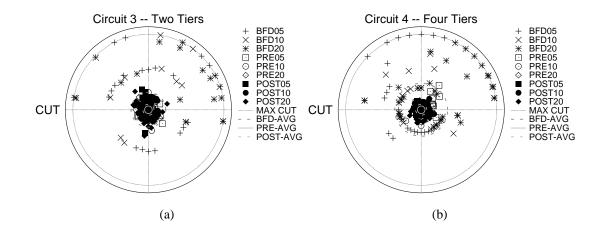

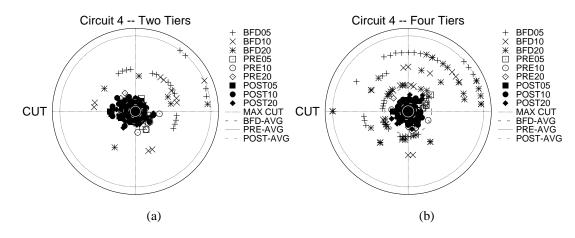

| Figure 24 | CTL results for circuit 1                         | 57 |

| Figure 25 | CTL results for circuit 2                         | 57 |

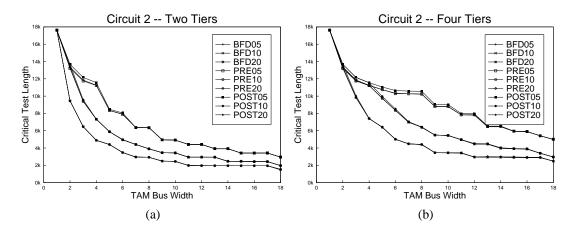

| Figure 26 | CTL results for circuit 3                                    | 58 |

|-----------|--------------------------------------------------------------|----|

| Figure 27 | CTL results for circuit 4                                    | 58 |

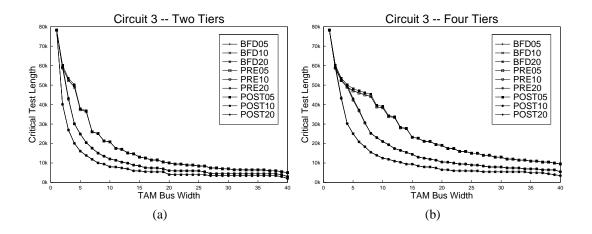

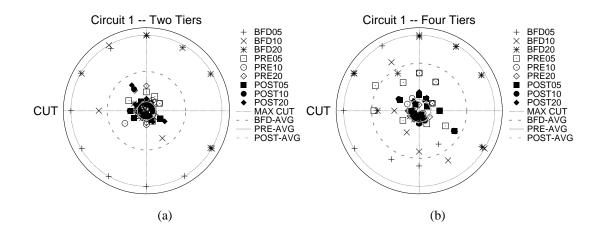

| Figure 28 | Cut results for circuit 1                                    | 60 |

| Figure 29 | Cut results for circuit 2                                    | 60 |

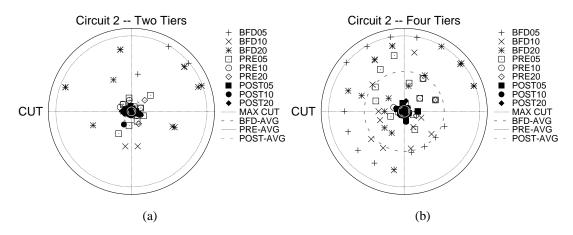

| Figure 30 | Cut results for circuit 3                                    | 61 |

| Figure 31 | Cut results for circuit 4                                    | 61 |

| Figure 32 | 3D via defect scenarios                                      | 64 |

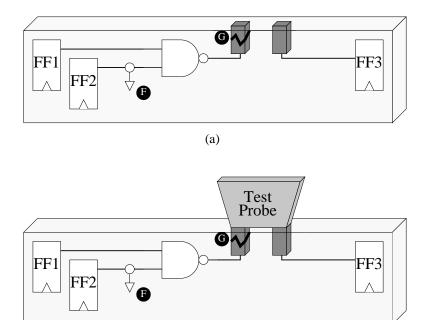

| Figure 33 | Motivation for shorting probes test methodology              | 66 |

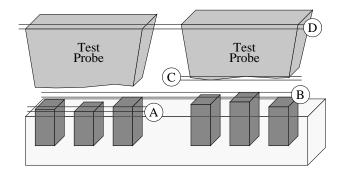

| Figure 34 | MEMS probe tip array                                         | 67 |

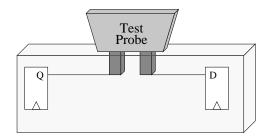

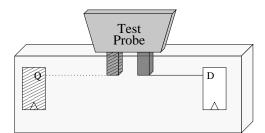

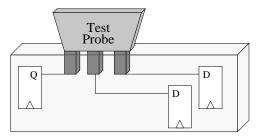

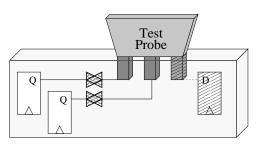

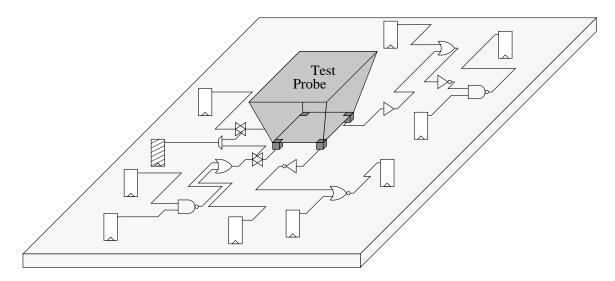

| Figure 35 | Example applications of the shorting probes test methodology | 70 |

| Figure 36 | Another example application                                  | 72 |

| Figure 37 | Generalized 3D via assignment plan                           | 73 |

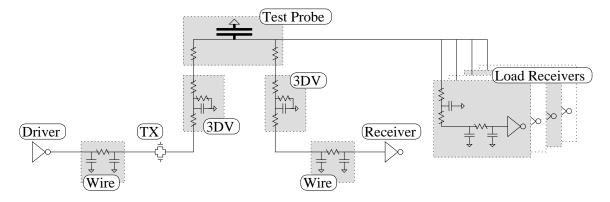

| Figure 38 | Shorting probes circuit model                                | 74 |

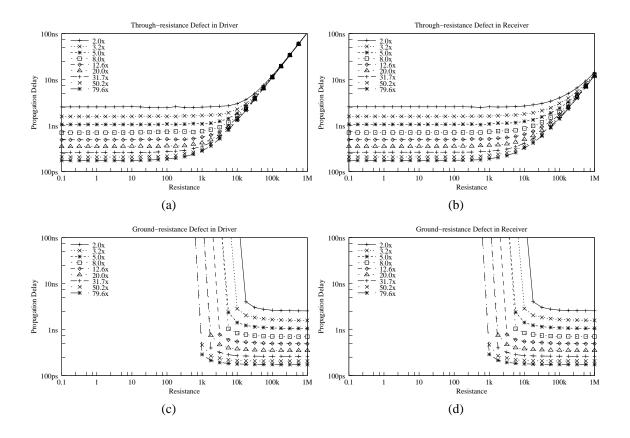

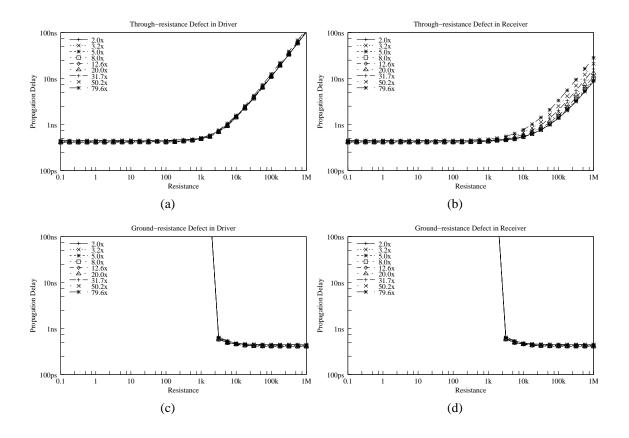

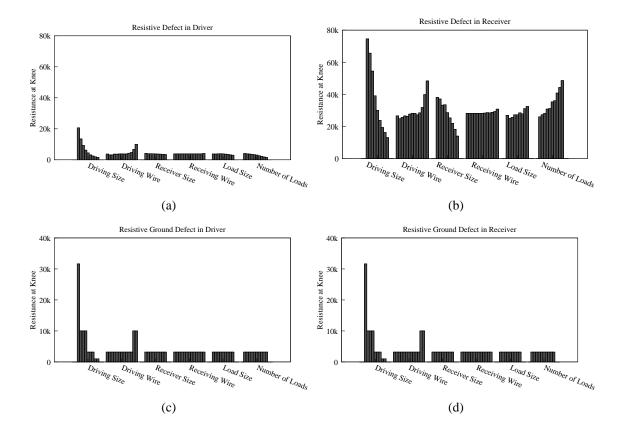

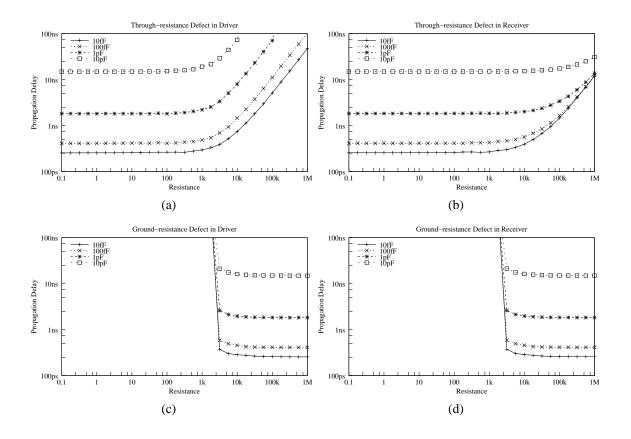

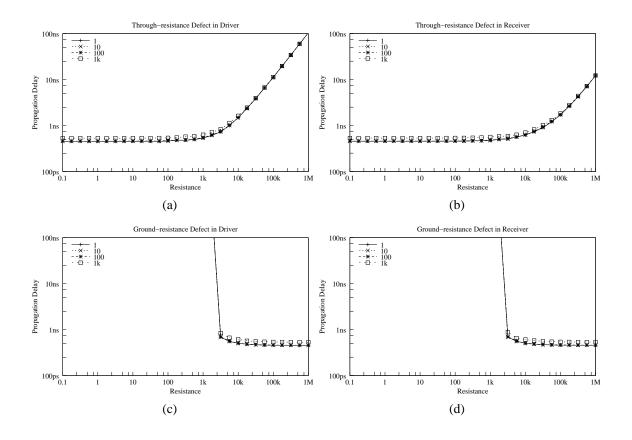

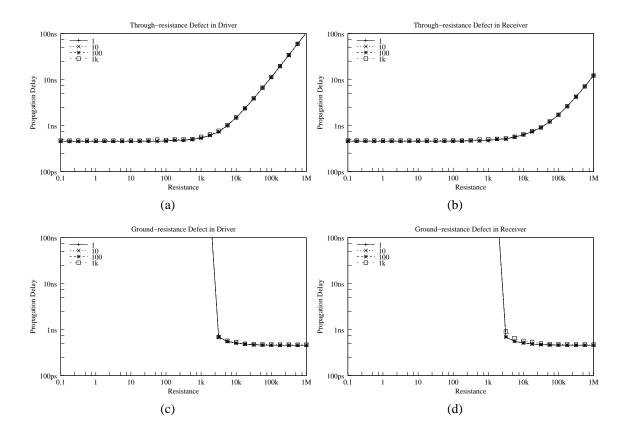

| Figure 39 | Sensitivity results for driver strength                      | 77 |

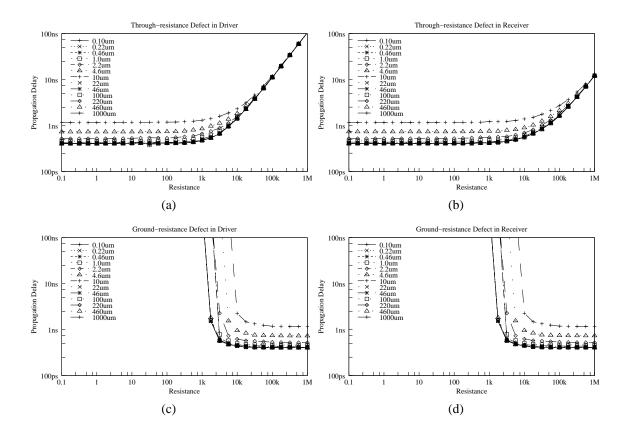

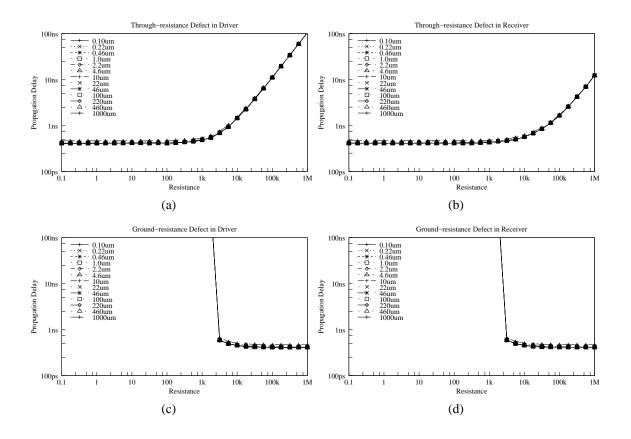

| Figure 40 | Sensitivity results for driver wire length                   | 79 |

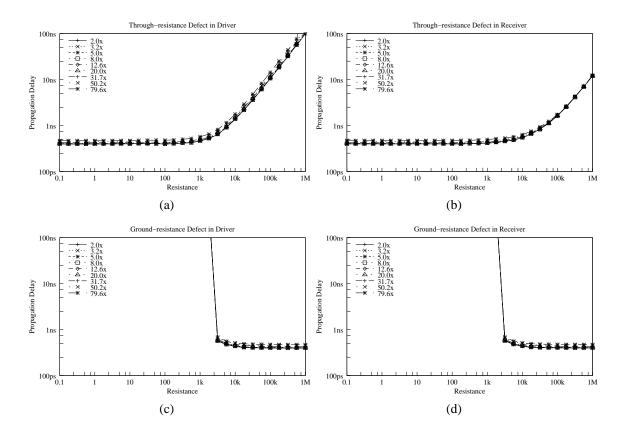

| Figure 41 | Sensitivity results for receiver strength                    | 80 |

| Figure 42 | Sensitivity results for receiver length                      | 81 |

| Figure 43 | Sensitivity results for load strength                        | 82 |

| Figure 44 | Sensitivity results for the number of loads                  | 83 |

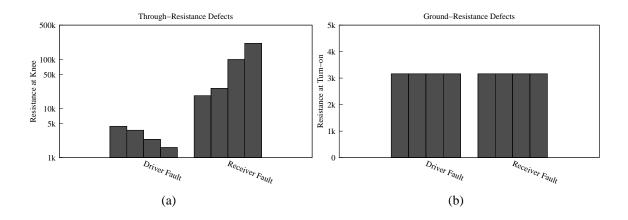

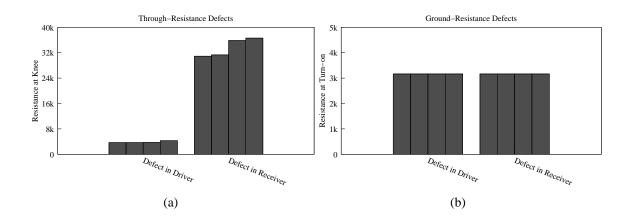

| Figure 45 | Knee-point results for sensitivity analyses                  | 84 |

| Figure 46 | Sensitivity results for probe tip capacitance                | 85 |

| Figure 47 | Knee and turn-on point results for probe capacitance         | 86 |

| Figure 48 | Monte Carlo distribution of propagation delays               | 87 |

| Figure 49 | 3D via variation sources                                     | 90 |

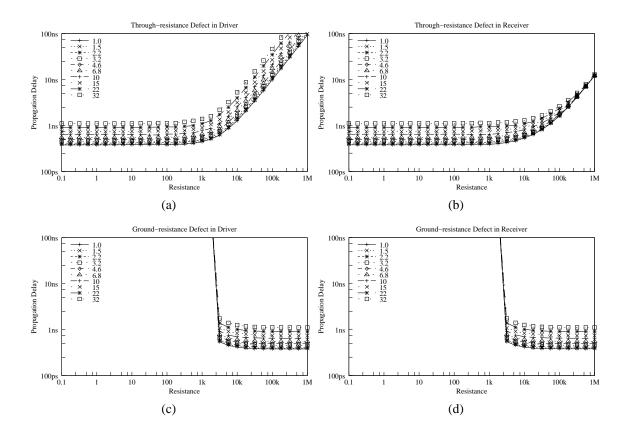

| Figure 50 | Sensitivity results for driver contact resistance            | 91 |

| Figure 51 | Sensitivity results for receiver contact resistance          | 92 |

| Figure 52 | Knee and turn-on results for contact resistance with driver  | 93 |

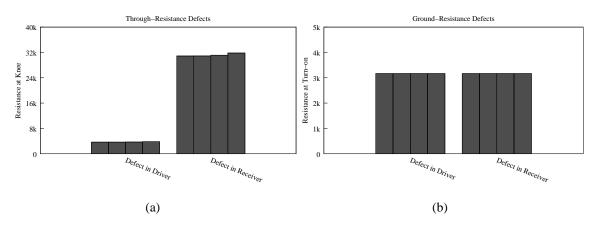

Figure 53 Knee and turn-on results for contact resistance with receiver . . . . . . 93

#### SUMMARY

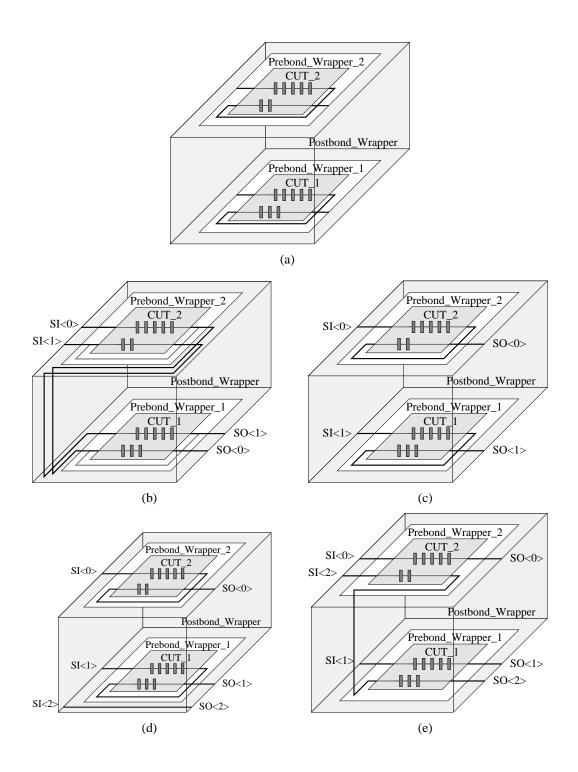

In this dissertation we describe several DFT techniques specific to 3D stacked IC systems. The goal has explicitly been to create techniques that integrate easily with existing IC test systems. Specifically, this means utilizing scan- and wrapper-based techniques, two foundations of the digital IC test industry.

First, we describe a general test architecture for 3D ICs. In this architecture, each tier of a 3D design is wrapped in test control logic that both manages tier test pre-bond and integrates the tier into the large test architecture post-bond. We describe a new kind of boundary scan to provide the necessary test control and observation of the partial circuits, and we propose a new design methodology for test hardcore that ensures both pre-bond functionality and post-bond optimality. We present the application of these techniques to the 3D-MAPS test vehicle, which has proven their effectiveness.

Second, we extend these DFT techniques to circuit-partitioned designs. We find that boundary scan design is generally sufficient, but that some 3D designs require special DFT treatment. Most importantly, we demonstrate that the functional partitioning inherent in 3D design can potentially decrease the total test cost of verifying a circuit.

Third, we present a new CAD algorithm for designing 3D test wrappers. This algorithm co-designs the pre-bond and post-bond wrappers to simultaneously minimize test time and routing cost. On average, our algorithm utilizes over 90% of the wires in both the pre-bond and post-bond wrappers.

Finally, we look at the 3D vias themselves to develop a low-cost, high-volume pre-bond test methodology appropriate for production-level test. We describe the shorting probes methodology, wherein large test probes are used to contact multiple small 3D vias. This technique is an all-digital test method that integrates seamlessly into existing test flows. Our experimental results demonstrate two key facts: neither the large capacitance of the probe tips nor the process variation in the 3D vias and the probe tips significantly hinders

the testability of the circuits.

Taken together, this body of work defines a complete test methodology for testing 3D ICs pre-bond, eliminating one of the key hurdles to the commercialization of 3D technology.

# CHAPTER 1 INTRODUCTION

Test is a constant challenge in the integrated circuit (IC) industry. Manufacturing processes are imperfect, yet customers expect working products, so IC manufacturers must, to the best of their ability, ensure that each part is correct before shipping it. The most prevalent modern test solution in digital systems is *scan* and its derivative technologies, which has been used with great success over the past couple decades to ensure final product quality.

Scan-based IC test is a simple idea: stitch all the internal flip-flops into a scan chain, then use this chain to insert test vectors and recover test responses. This provides direct access to the internal logic, greatly simplifying and expediting the testing process. From this basic idea, an entire field of research and development has arisen and lead to key innovations such as built-in self-test, memory self-test, test-time optimization algorithms, black-box-IP self-test, and analog and mixed-signal test. All these are built upon the foundation of scan test.

Underpinning the effectiveness of scan testing is a set of basic IC features, elements of digital IC designs that are critical to execution of a scan test. Some of these features include

- Connected and operational signal nets (i.e., each net has at least one driver and one receiver)

- Connected and operational master signals such as clock and reset

- Connected and operational power and ground rails

- Large off-chip bonding pads for test access

Unfortunately, when we consider the application of scan test to 3D integrated IC chip stacks, we find that many of these basic features are missing within the unbonded dies. All 3D signal nets will necessarily be missing either the driver or the receiver pre-bond,

breaking the test paths; with highly-optimized 3D designs, master signals are fragmented and useless pre-bond; and the large off-chip bond pads exist only on the top tier and so are unavailable to all other tiers pre-bond. In fact, the only feature listed above that can be counted upon is the power and ground rails, which are so ubiquitous in every IC that they remain fully connected even in partitioned 3D designs.

For the rest, new *design-for-testability* (DFT) structures are required to either restore or replace these missing features. DFT is a general design philosophy wherein the ease and effectiveness of product test is considered as a primary requirement throughout the design process. In the case of 3D ICs, the requirements of pre-bond test must be considered from the outset. An unbonded 3D tier is a completely unique target device, unlike any before it. This is because, at the most fundamental level, an unbonded tier is a broken device; part of the basic circuit functionality is located on the neighboring tiers, not on the tier-undertest. This necessitates new testable designs that are specific to 3D IC stacks, and this is the challenge we take up in this book.

The remainder of this book is organized as follows. Chapter 2 presents the details of the 3D test problem and the prior art that forms the foundation of the DFT solutions presented later. Chapter 3 describes a new 3D-aware test architecture and demonstrates its application to a real 3D IC design. Chapter 4 describes extensions to this test architecture for circuit-partitioned 3D designs. Chapter 5 describes a new tool that extends test wrappers, a very successful DFT technique used in planar SOCs, into the third dimension. Chapter 6 describes a brand new technique for testing the 3D structures themselves pre-bond. Chapter 7 summarizes recent developments from other research groups in the field of 3D test. Chapter 8 concludes.

#### **CHAPTER 2**

#### **ORIGIN AND HISTORY OF THE PROBLEM**

The problem we will study in this book is a product of the collision of two fields: 3D integration and testable circuit design. 3D integration is an exciting new manufacturing technology in which multiple silicon chips are stacked vertically to decrease communication distance while increasing total silicon area. However, it creates significant challenges for test, especially in the unbonded tiers. We will examine both fields in turn.

#### **2.1 Design for Test**

Manufacturing is an errant activity, no matter the industry, and it generally makes good economic sense to test products to ensure final quality (that is, the percentage of working parts out of all product shipped). Due to the incredible complexity of modern ICs—just a single stage in a current generation processor might have 2<sup>128</sup> possible states—designing chips for testability is a basic necessity. The field of *design for test* (DFT) got its start in the 1970s as IC complexity pushed into large and then very-large scale integration. We will examine the key milestones in the development of DFT here.

#### 2.1.1 Scan Test

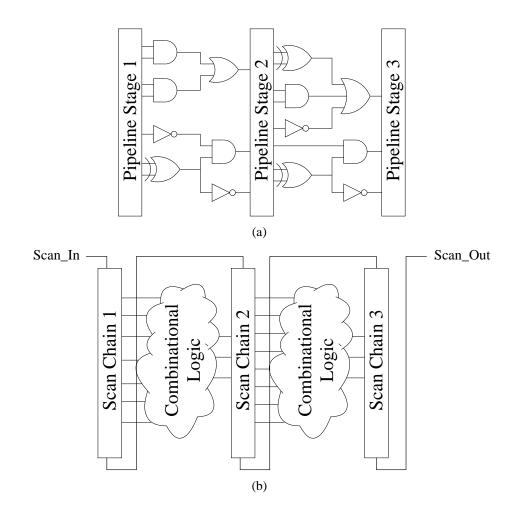

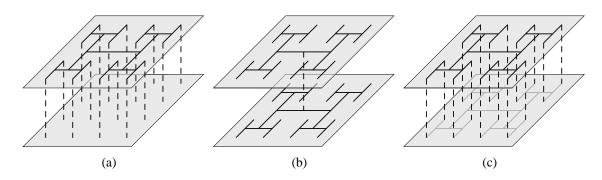

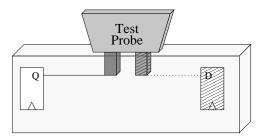

The most fundamental concept in DFT is scan. The idea is to give an IC two operational modes, *functional* and *scan*, as shown in Figure 1. Functional mode is the normal operative mode of the chip, where it performs the task for which it is designed. Scan mode is the test mode of the chip, where all components are, ideally, reduced to two sets: combinational logic and scan registers. By scanning data into all the registers, the tester gains complete and immediate control of the entire system state, significantly reducing the complexity of test.

Of course, scan is not a complete answer to the IC test problem, for two primary reasons. First, the bandwidth of a scan chain is very limited. Second, only a subset of circuit

Figure 1. The two operational modes in a simple IC with DFT:(a) functional mode and (b) test mode.

design techniques and technologies can be fit into the "combinational logic or scan register" abstraction. To address these short-comings, *built-in self test* (BIST) techniques have been developed.

Limited scan bandwidth is generally addressed with a combination of parallelization and test data compression. Unfortunately, the former is limited by the number of package pins available, so even modern ICs have only a few dozen parallel scan paths [51, 70, 77]. More significant test time reductions come from test compression. A BIST implementation of test compression most often relies on linear feedback shift registers to create *pseudo-random pattern generators* (PRPGs) and *multiple input signature registers* (MISRs). PRPGs generate random test data to drive the *circuit under test* (CUT), and MISRs compress the CUT response into a signature. With these components, the tester needs only to scan in the initial PRPG state and scan out the final signature for comparison, reducing test data load many-fold. The *built-in logic block observer* [39] (BILBO) is perhaps the most complex implementation. It combines the functions of a register stage, scan chain, PRPG, and MISR into a single bank of flip-flops.

For circuits that do not fit the scan abstraction, more application-specific test designs are necessary. The most important, and so most studied, class of these circuits is memory, leading to a entire subfield of BIST research called *memory BIST* (MBIST). Memory represents unscannable IC state, so MBIST techniques must work with the addressing features of the memory system to successfully execute memory test. This generally consists of a carefully-designed pattern of reads and writes to activate various possible faults. Two example sequences are the *Algorithmic Test Sequence* [38] (ATS) and *Galloping 1's and 0's* [13] (GALPAT) though there are certainly many more [6]. ATS detects all stuck-at faults in a memory, while GALPAT extends this fault coverage to include all coupling faults between memory cells as well. Most MBIST algorithms range between O(n) and  $O(n^2)$  complexity, where *n* is the number of memory cells; applying that many patterns one at a time through scan is simply economically impossible for any reasonably-sized memory but is very feasible with BIST.

#### 2.1.2 Modular Test

Of course, verifying the operation of the component ICs is not sufficient to guarantee a working computer system. The motherboard and other PCBs are also critical. Originally, PCBs were tested with probes. The tester would touch each end of a PCB wire with probes to verify it was manufactured properly. But this is not cost-effective in modern PCBs which can have many thousands of wires. To address this problem, the *boundary scan register* (BSR) was developed in the 1980s and formalized in 1990 as the IEEE 1149.1 standard [3]. The BSR is just a scan chain which contains a scan cell for every signal pin in or out of an IC. To test a PCB bus between two ICs, the manufacturer needs only to scan

the test data into the BSR of one IC and then read that same data out of the BSR of the other IC. Most importantly, the IC vendors do not need to surrender any of their IP to the PCB manufacturer to enable this test (other than a description of the BSR).

The 1149.1 standard also describes a *test access port* (TAP)—the TAP chiefly contains a state machine, a command register, and multiplexers—that must be used to interface the BSR to the PCB's test architecture. With this TAP in place, IC vendors realized they could also use it to access internal IC test features after system integration. This enabled the vendors to ship test bit streams with their products. The PCB manufacturer could then apply these bit streams to the TAP and verify the correctness of the IC, all without knowing the actual details of the IC. This created a robust system of modular testing (or *black box testing*) of components to verify the final product.

A collection of test resources such as those defined in 1149.1 is known as a *test wrapper*. The chief function of a test wrapper is to create boundaries within the test architecture for isolating different modules from one another, allowing them to be tested independently. 1149.1 test wrappers, for example, allow ICs and the buses that interconnect them to all be tested independently.

With the advent of *systems-on-chip* (SOCs) and other products of similar complexity, the concept of the test wrapper was adapted to in-chip test as well. Now instead of isolating ICs and PCB buses from one another, the goal is to partition the chip itself into several modules that can then be tested individually. In a true SOC, the IP blocks define a natural partitioning scheme; in monolithic ICs, chip functionality can define the scheme (for example, isolating the processing core from the various units of the memory hierarchy). Test wrappers for SOCs were formalized in 2005 in the IEEE 1500 standard [4].

Adapting test wrappers to SOCs was not straightforward. Because of the limited amount of data required to test buses between ICs, the 1149.1 standard calls for a single one-bit test data bus. The 1500 standard however was designed from the start for both testing the buses between IP blocks and for testing circuits internal to the IP. This requires a much greater

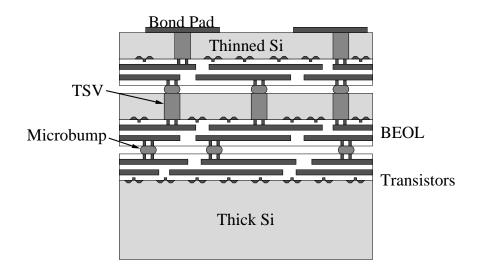

Figure 2. A 3D integrated die stack.

test data volume. Therefore, the test architecture problem expanded to include the design of the *test access mechanism* (TAM), the multi-bit test bus used to interconnect the test data ports on each test wrapper. An SOC test architecture may include just one wide TAM or many skinny TAMs, whichever minimizes the test cost. This makes the effort of designing a test architecture for 1500 test wrappers much more difficult than for 1149.1 test wrappers.

Now this cycle of modular test design must begin again, this time for 3D ICs.

#### 2.2 3D Integration

3D integration (shown in Figure 2) is an emerging technology that allows semiconductor die to be bound together to form a tightly integrated stack. Opening design to the third dimension provides several advantages. First, it enables the integration of heterogeneous components such as logic and DRAM memory [11, 71] or analog and digital circuits [9]. Second, it increases routability [65]. Finally, it can substantially reduce wire length, which contributes to both long communication latency and to high power consumption. Recent work in this field has already demonstrated significant improvements in both performance and power consumption [69, 83] and lead to other interesting applications, such as on-line profiling [54] and network-in-memory [43], and even greater returns are expected as

researchers further explore the opportunities afforded.

#### 2.2.1 Die Stacking

3D stacking replaces the long, heavily-loaded interconnects of present day integration schemes—for example multi-chip modules or package-on-package stacks—with short, fast 3D vias (which may be backside TSVs, faceside microbumps, or a combination of both). 3D via manufacturing lines already exist which can produce vias approximately one micron in diameter, and companies are pushing into the submicron domain, testing  $0.4\mu$ m 3D vias [64].

#### 2.2.2 3D Partitioning Granularity

Die stack technology may be used to partition a design at three general levels of granularity. The coarsest level is the technology level. Disparate technologies like high-speed CMOS and high-density DRAM both have their own dedicated and highly-optimized manufacturing processes. Many problems arise when attempting to integrate such technologies onto a single die, requiring sophisticated manufacturing tricks to achieve economically viable integration quality [60]. Die stacking allows each technology to be manufactured on its own tier in its own process. After each tier is manufactured, a separate integration process bonds these tiers together. The result is the best of both worlds: each tier is manufactured at the highest possible quality level and, simultaneously, the two technologies are tightly integrated. This improves both the performance of the system and the form factor.

The next finer level of partitioning is the architectural level. Unlike technology partitioning, both tiers are manufactured using the same process. The goal of architectural partitioning is to spread the functional blocks of a design across the available tiers in such a way as to minimize the length of the interconnect buses. By reducing bus length, the resistance and capacitance seen on these buses is reduced, consequently reducing power consumption and improving performance. Architectural partitioning makes much better use of the large number of 3D vias available than technology partitioning. The finest partitioning granularity is the circuit level. Here, the transistors that make up a functional block may exist on different tiers. Circuit partitioning has its own levels of granularity. At one extreme, blocks are simply split along logical boundaries into subblocks (e.g. a design could place half the banks of a cache on one tier and the other half on a different tier—so called bank-stacking [43, 66]). At the other extreme, individual circuits are split across the tiers (e.g. in a register file, read and write ports may be spread across different tiers, connected to the actual memory inverter pair through 3D vias; this is known as port splitting [69]). This granularity best utilizes the available 3D vias and thus shows the best power and performance improvements.

#### 2.3 3D Testing

The problem we address then is enabling test in a 3D integrated chip stack. There are three different test situations to consider:

- 1. *Pre-bond* a single tier is under test which is not bonded to any other tier

- Partial-stack some incomplete subset of the chip stack is under test, including the bonds between the tiers in this subset

- 3. Post-bond also final stack, the entire completed chip stack is under test

Post-bond test is the least interesting case. Once the chip is complete, all chip components are existent and functional, so the situation is identical to that of bare-die test in traditional planar manufacturing lines. Pre-bond and partial-stack tests are much more interesting and challenging because some of the chip functionality is necessarily missing. Additionally, the 3D vias represent dangling nets, which are a challenge unique to 3D.

To enable pre-bond test<sup>1</sup> then, we require DFT features both to compensate for missing functionality and for establishing controllability and observability over dangling 3D connections. The work presented in Chapters 3, 4, and 5 addresses these issues for the circuitry

<sup>&</sup>lt;sup>1</sup>Hereafter we refer only to pre-bond test rather than both pre-bond and partial-stack test because both face the same key challenges and benefit from the same solutions.

internal to each tier. The work presented in Chapter 6 presents a methodology for testing the 3D vias themselves pre-bond.

#### **CHAPTER 3**

#### PRE-BOND TEST ARCHITECTURE AND APPLICATION

The overall DFT plan for a chip is called the *test architecture*. The test architecture is the chip-wide master plan the organizes and manages all the various DFT components within the chip and provides an off-chip interface for test execution. It is through the test architecture that the multitude of scan chains, BIST engines, test wrappers, and other test features are accessed.

Generally, test architectures are designed to rely on the correct operation of as few chip features as possible because if the test architecture fails, the chip is effectively worthless, even as a trouble-shooting tool. These features include such things as a working clock, properly-charged power rails, a set of operational control signals (*reset*, *test\_enable*, *clk\_ctrl*, etc.), and a minimum number of functional I/O pins (usually just four).

By-and-large, these are fairly simple needs, and of course that is the point of designing the test architecture in such a manner. 3D integration, however, adds a new twist to the story, which we will explore in this chapter.

#### **3.1 Requirements**

There are several requirements a pre-bond test architecture must meet in order to successfully enable pre-bond test. We examine these requirements and the challenges each addresses here [40].

#### **3.1.1** Completing the Design

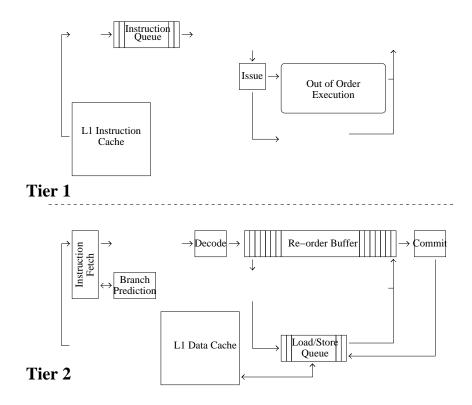

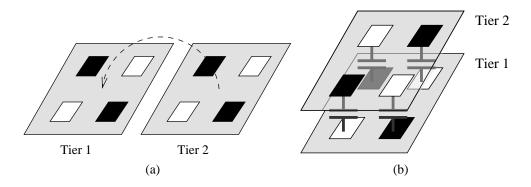

The primary testability challenge posed by 3D integration is that, pre-bond, each tier exists in an incomplete state. For a technology partitioning, there is no problem, as each tier is by definition functionally complete. For an architectural partitioning (for example, the partitioning of a processor core shown in Figure 3) however, there are problems. Traditional test methodologies [10, 51, 63, 70, 77] can depend on full connectivity within the chip,

Figure 3. Example partition a generic out-of-order processor across two tiers.

especially in functional or partial-scan test, but this connectivity is not guaranteed in a 3D IC pre-bond. The situation is exacerbated by circuit-level partitionings wherein even the functional blocks are incomplete, and, worse, the circuits themselves may be incomplete and functionally broken. This leads to a paradox of sorts in that we want to test broken circuits to see if they function correctly [41]. Testing circuit-paritioned 3D designs will be discussed in Chapter 4.

The simple brute-force solution would be to probe each 3D via individually, providing or observing test values as necessary. Unfortunately, this will not work for pre-bond test; the number of 3D vias on a given tier can vary from hundreds to hundreds of thousands, and no probe card can provide that many test channels [81]. Therefore, a pre-bond DFT architecture must either replace the missing connections or enable new methodologies for testing without them.

#### **3.1.2** Test Hierarchy

The pre-bond DFT architecture does not exist in a vacuum. Post-bond test, package test, and so on will follow. Therefore, to keep the cost of test down, the pre-bond test architecture must be designed to integrate with the test architectures for these other methods and provide maximum reuse of test modules.

#### 3.1.3 Hardcore

The *hardcore* of a chip is its infrastructure, nets like power, ground, clock, and reset that must be complete and functional for the tier to be able to work by any definition. Any DFT architecture must carefully consider these nets to make sure they are fully connected and operational.

#### 3.1.4 External Access

While the 3D vias cannot be individually probed, some sort of external access via test probes and pads is required to both power the tier hardcore and provide the test access. In all but the top tier of the die stack, these pads must simply be buried post-bond. Thus, the DFT architecture must use this resource very judiciously to control the area cost.

#### 3.2 Hardware

Here we present our 3D DFT architecture and examine how it meets the requirements laid out.

#### 3.2.1 Tiers as Test Modules

As mentioned previously, modular test with test wrappers is a very popular technique. Independent test modules has been successfully applied in many large ICs; an example is the Alpha 21364, which was partitioned with test wrappers into what the Alpha team called *scan islands* [10]. Data would flow freely between islands in functional mode. In test mode however, the test wrappers closed the borders between islands, replacing the

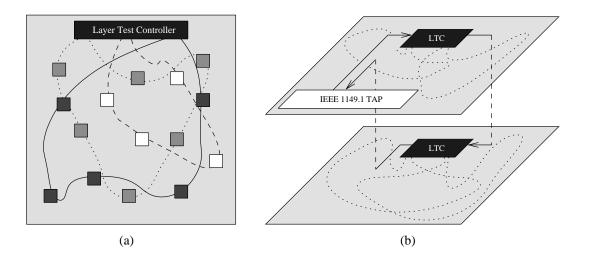

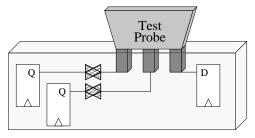

Figure 4. Our 3D test architecture. (a) shows a single tier with connections from the LTC to the various scan chains. (b) shows the LTCs integrated into the chip-level test architecture.

functional signals with test signals from the scan chain. By segmenting the design into several testable modules, such designs significantly reduce the cost and complexity of test.

Comparing this approach to 3D designs, it is clear that each tier, before bonding, exists as a perfectly isolated test module—a condition the Alpha designers were not able to achieve. Thus we adopt this general test strategy to design our pre-bond test architecture, essentially enclosing each tier in its own test wrapper. The central feature of these tier wrappers is the *Layer Test Controller* (LTC), which manages access to the scan chains on the tier (or to lower-level test wrappers if they are in use). Figure 4(a) shows a generic 3D tier with scannable registers hooked up into three scan chains controlled by an LTC. Note that scan cell ordering is well-studied problem [8, 12, 28, 47] and so is not considered here.

Critically, the LTC patches nicely into next higher-level wrapper in the test hierarchy (Figure 4(b)). This satisfies our second requirement and allows for the resources created for pre-bond test to be reused in subsequent test.

To complete our test architecture, the dangling 3D nets must be tied off. As in the prior art, we accomplish in most cases by inserting boundary scan cells as appropriate, satisfying the primary requirement a pre-bond test architecture. These scan cells are necessarily gated so that they do not compete with the 3D-via-connected sources post-bond.

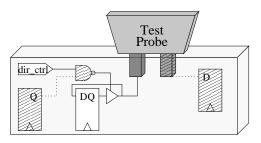

Figure 5. Three 3D clock trees. (a) is optimized for wire length and power consumption while (b) is optimized for pre-bond testability. (c) is the best of both.

#### 3.2.2 Tier Hardcore

None of the features of our test architecture are of any use without the test hardcore, the third pre-bond test requirement. The power and ground rails are not a concern. These rails are so ubiquitous and so heavily utilized that they will always be fully connected in every tier. This observation is confirmed by the 3D-MAPS test chip [27].

This is not so for other hardcore signals, generally any signal such as clock or reset which are wire length limited. These nets benefits greatly from 3D design, significantly reducing wire length and power consumption [53]. Figure 5(a) shows an H-tree design for clock distribution in a 3D chip stack. Note that the tree exists almost entirely in the upper tier while 3D vias provide local clock connectivity on the bottom tier. This greatly reduces the cost of the clock, but the many small clock trees on the bottom tier are completely useless for pre-bond test.

An alternative, test-friendly clock tree is shown in Figure 5(b). The clock is fully connected on every tier and so can be used for pre-bond test. However, the cost of the clock is much greater in this design because of the large amount of redundancy in the distribution network.

Our solution is a hybrid design as shown in Figure 5(c). This design is comprised of a 3D-optimized main clock tree (in black) and a pre-bond test tree (in gray). Not shown are tri-state buffers which must be located at each leaf of the pre-bond tree to disconnect it

Figure 6. A power rail test pad arrangement that is post-bond reuse aware.

post-bond. Such a design both enables pre-bond test but also saves clock power post-bond, at the cost of bottom-tier routing resources. For stacks greater than two, a pre-bond tree is necessary for each tier. Hybrid 3D clock trees were fully evaluated by Xin et al. in [85, 86]. They created a CAD tool to design these trees and reported power savings around 20%.

#### 3.2.3 External Access

Probe pads, as stated, are unavoidable. The use of test wrappers significantly reduces the number of pads required (the LTC requires a similar test access width as 1149.1 and 1500, four signals minimum). But to simply bury these pads post-bond is wasteful. We propose reusing them as *decoupling capacitors* (decap) as shown in Figure 6. If the pads are already tied to power and ground rails, nothing more is required than to line them up (the pad pattern shown is recommended since the same probe card can be used for each tier). If the pads are tied to other signals, a simple fuse or similar circuit element can tie them to one of the rails post-bond.

# **3.3 Experiments3.3.1 Architectural Partitioning**

Our experiments are based on the architecture and technology of the Alpha 21264. In order to evaluate the cost of implementing our pre-bond test strategy, we need to know the area consumed by a scan cell and the number of scan cells required in a 3D-integrated design.

To determine a realistic size for the scan cell, the scan cell was laid out using  $0.25\mu m$

Figure 7. A floorplan for a two-layer die stack split by architectural block. The gray areas between and around blocks represents whitespace within the floorplan.

TSMC design rules. This technology generation was selected to match, as closely as possible, that used to manufacture the 21264A. The actual design of the scan cells is based on the 8T latch. Each cell requires  $75.8\mu m^2$  of silicon.

To determine the number of cells required by our technique, a sample 3D floorplan (Figure 7) for a 21264 was designed by a published 3D floorplanner [82]. From this floorplan we extracted the number of signals crossing between the die. Table 1 lists all of the inter-die buses, the number of signals comprising that bus, and the cost of adding the necessary scan cells. Note that each signal requires two scan cells: one on the source side to observe the test output and another on the sink side to provide a test input.

The bottom row in Table 1 gives the final area cost of injecting and observing test values on 3D signals. This cost is 0.165% of the area of the sample floorplan in Figure 7. However, the floorplan contains 8.56% whitespace, so the scan flops do not require an expansion of the chip footprint. Additionally, the area consumed by the scan flops is only 0.173% of the die size of the original Alpha 21264A, which results in a negligible expansion of the die footprint.

| SOURCE               | Tier | SINK                 | Tier | BITS | <b>AREA</b> $(\mu m^2)$ |

|----------------------|------|----------------------|------|------|-------------------------|

| Instruction Cache    | 1    | Instruction TLB      | 2    | 40   | 6065                    |

| Instruction TLB      | 2    | Instruction Cache    | 1    | 174  | 26384                   |

| Instruction Cache    | 1    | Fetch and Decode     | 2    | 128  | 19409                   |

| Fetch and Decode     | 2    | Instruction Cache    | 1    | 42   | 6369                    |

| INT Mapping          | 2    | INT Queue            | 1    | 200  | 30326                   |

| INT Queue            | 1    | Issue                | 2    | 196  | 29720                   |

| INT Register File 1  | 2    | INT Execution Unit 2 | 1    | 150  | 22745                   |

| INT Execution Unit 2 | 1    | INT Register File 1  | 2    | 71   | 10766                   |

| INT Execution Unit 2 | 1    | INT Mapping          | 2    | 14   | 2123                    |

| INT Execution Unit 2 | 1    | Branch Predictor     | 2    | 93   | 14102                   |

| INT Register File 2  | 2    | INT Execution Unit 4 | 1    | 150  | 22745                   |

| INT Execution Unit 4 | 1    | INT Register File 2  | 2    | 71   | 10766                   |

| INT Execution Unit 4 | 1    | INT Mapping          | 2    | 14   | 2123                    |

| INT Execution Unit 4 | 1    | Branch Predictor     | 2    | 93   | 14102                   |

| FP Register File     | 2    | FP Execution Unit 1  | 1    | 154  | 23351                   |

| FP Execution Unit 1  | 1    | FP Register File     | 2    | 71   | 10766                   |

| FP Execution Unit 1  | 1    | FP Mapping           | 2    | 14   | 2123                    |

| Load/Store Queue     | 2    | Data TLB             | 1    | 66   | 10008                   |

| Load/Store Queue     | 2    | Data Cache           | 1    | 180  | 27294                   |

| Data Cache           | 1    | Load/Store Queue     | 2    | 144  | 21835                   |

| Data Cache           | 1    | Memory Controller    | 2    | 166  | 25171                   |

| Memory Controller    | 2    | Data Cache           | 1    | 166  | 25171                   |

| TOTAL                |      |                      |      | 2397 | 363,461                 |

Table 1. This list consists of the buses that cross from one tier to another. Listed are the source block and tier, the sink block and tier, the number of signals, and the area penalty paid to include scan flops.

Our experiments assume a simple LTC design. The LTC provides parallel access to sixteen scan chains per layer. Additionally, the LTC contains sixteen one-bit bypass registers. Finally, sixteen multiplexers and demultiplexers are included to allow selection between the scan chains and the bypass registers. Together, this allows for sixteen scan chains per layer—thirty-two chains in the chip—which is comparable to modern designs [70]. This design requires thirty three test pads per layer:  $S_i[15,0]$ ,  $S_o[15,0]$ , and a select signal. The area cost of such an LTC is insignificant compared to the cost of the injection and observation scan cells.

This area cost represents the worst-case cost we should expect for implementing this test technique for two reasons. First, academic layouts produced under publicly available

Figure 8. A schematic of 3D MAPS chip stack, showing the sixty-four cores, sixty-four SRAM tiles, and 3D connections.

DRC rules are much larger than functionally-equivalent industrial designs produced under highly-optimized and proprietary DRC rules. Second, we assume a worst-case scan cell scenario in which *every* 3D via requires the addition of two scan cells that serve no purpose beyond pre-bond test value injection or observation. In a real design, many of these cells could be unnecessary—if the 3D via directly sources and/or sinks a scannable flip-flop—or could be reused as part of the post-bond test strategy. For these reasons, we expect an actual application of our technique in an industrial design to cost even less area than the results reported here.

#### **3.4 3D-MAPS Test Architecture**

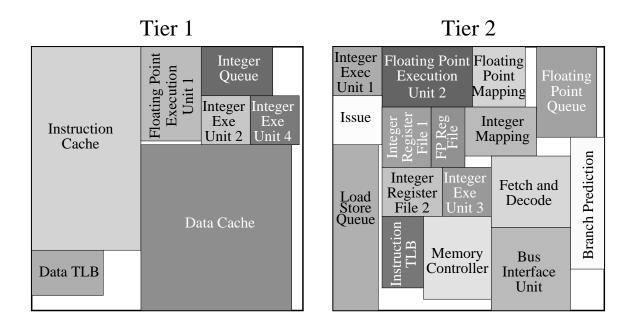

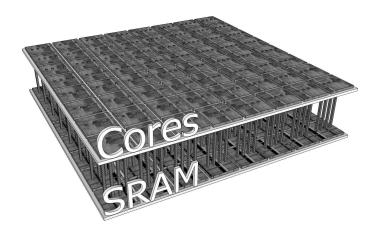

The 3D Massively Parallel Processor with Stacked Memory (3D-MAPS) chip is a test vehicle for evaluating the benefits of 3D fabrication. The design goal was to produce a processor that could consume as much 3D bandwidth as possible and demonstrate the performance improvements expected of applications running on such a system.

The test architecture in the 3D-MAPS chip is based on design-for-pre-bond-test principles that have presented in this chapter, so here we present the details of 3D-MAPS as a case study in pre-bond-testable design.

Figure 9. An annotated SEM image of the 3D-MAPS chip showing the key 3D components: backside I/O pads, TSVs, thinned top tier, and the microbump face-to-face bond.

#### 3.4.1 3D Processor Design

#### 3.4.1.1 Chip Stack

The basic architecture of 3D-MAPS is shown in Figure 8 while an image of the actual 3D-MAPS chip stack is shown in Figure 9. The stack consists of two tiers (5mm on a side for  $25\text{mm}^2$  of silicon per tier or  $50\text{mm}^2$  total) bonded face-to-face with microbumps (3.4 $\mu$ msize,  $5\mu$ mpitch). Global Foundries [25] fabricated the front-end-of-line (130nm bulk-Si), TSVs (via-first process;  $1.2\mu$ msize,  $2.5\mu$ mpitch), and back-end-of-line (six metals). The thick (765 $\mu$ m) wafers were shipped to Tezzaron Semiconductor for finishing, including bonding (thermo-compression), thinning ( $12\mu$ mtotal, composed of  $6\mu$ mbulk and  $6\mu$ mBEOL), I/O pad deposition, and dicing. The I/O pads are placed on the backside of the thinned die (235 I/Os; 14 carry signals, the remainder are power and ground). 204 TSVs are used per I/O cell to handle off-chip current loads.

#### 3.4.1.2 Architecture

3D-MAPS is composed of sixty-four processors and sixty-four SRAM data memories (one private memory per processor). A 116b 3D bus connects each processor to its memory. Each core is a five-stage, in-order, two-wide VLIW machine. The two-instruction format was chosen to maximize utilization of the 3D bus; each core can execute a memory instruction every cycle, for a total 3D bandwidth of 71GBps at 277MHz operating frequency.

Within each core is a 1.5kB instruction memory (192 bundles) and a 1kb register file. Each memory tile is composed of four 1kB memory banks. That is 4kB of data memory per core and 256kB total in 3D-MAPS.

Figure 10. General test sector architecture. Shown are the sixty-four cores divided into four sectors, the twelves scan chains (three per sector), and the 3D interface between the tiers.

For communication, 3D-MAPS has an eight-by-eight mesh network. Each processor can pass data to its four neighbors. This mesh provides 8.9GBps bisection bandwidth. There is no communication between memory tiles; coherency must be maintained by the programmer. A barrier instruction is provided for synchronizing the cores.

#### 3.4.1.3 Off-chip Interface

The functional off-chip interface is limited to three bits, which are physically multiplexed onto the test pins. These three are *done*, *barrier\_req*, and *barrier\_ack*. *done* signals the end of computation, and *barrier\_req* signals that all cores have reached the barrier. Both of these signals are produced by AND trees that reduce the individual *done* and *barrier\_req* signals of the sixty-four cores to a single output. *barrier\_ack* is a control signal which provides breakpoint-like functionality and discussed further in Section 3.4.2.3.

#### 3.4.2 Sector Test Architecture

The test architecture design process had two goals: graceful degradation and easy experimentation. Graceful degradation is the ability of the design to isolate faulty, failing portions of the chip from good, functional portions of the chip. Graceful degradation is particularly important to this design because 3D integration is a largely untested manufacturing process, and we need to be able to make measurements with the chip even in the presence of many faults. Easy experimentation is the ability to control and observe the workings of the chip on deep, simple level.

To achieve these goals, we choose a sector-based full-scan test architecture, as shown in Figure 10.

#### 3.4.2.1 Graceful Degradation

A *sector* is a set of sixteen cores which are designed to test and operate independently of all other cores. Each sector is independent from the core level all the way up to the off-chip interface. This provides coarse-grained graceful degradation because a fault within a sector disables only that sector, not the entire chip.

There are a few key aspects to isolating a sector. First, each sector can disable the onchip mesh network at the boundary of the sector. When the boundary is closed, the sector receives all zeros on that link, rather than faulty communications. This behavior matches the boundary behavior of the full, eight-by-eight mess.

Second, each sector has independent AND-reduce trees for the *done* and *barrier\_ack* signals (Figure 10 shows one AND tree in the middle of each sector). In the final stage of reduction, each sector's signal is masked by a sector disable bit. This prevents a faulty sector from interfering with these reductions.

Third, each sector has an independent set of scan chains, as represented by the three thick wires in each sector in Figure 10. No sectors share any part of their scan chains, so a fault in a single scan chain disables only the sector in which that scan chain is found.

Finally, each sector has an independent pair of I/O test pads (shown on the left side of Figure 10. The scan chains for each sector are tied to that sector's I/Os so that even at the off-chip interface, the sectors are independent. Therefore if one of the pads is faulty, only the associated sector is lost; the others can still be subjected to experimentation.

As shown in Figure 10, 3D-MAPS is composed of four sectors. Four was chosen due

to area and pin-count constraints; fewer sectors would have provided too little graceful degradation, and more would have required too much area to implement.

The only hardware shared between the sectors in the hardcore and the test control. The hardcore consists of the power and ground rails, the clock tree, and the reset signal. The test control is composed of the test control state machine (TCSM) and the various enable signals it produces; test control is discussed in detail in Section 3.4.2.3. Isolating this hardware between sectors would have incurred much too high an area and design complexity cost to implement effectively. It is important to note that that communication between the sectors and this shared hardware is one-way;<sup>1</sup> a fault within a sector cannot propagate up through the shared hardware to fail the chip. A fault in the shared hardware itself could fail the chip, but the area of this hardware is quite small and so is an acceptably small failure risk.

#### *3.4.2.2 Easy Experimentation*

The other primary goal of the DFT design was ease of experimentation. We need to easily get deep into the chip and observe the various pathways. Most important is the 3D interconnect between the tiers, though general access to all paths is preferred. This is most simply achieved with a full-scan test solution. This provides simple, direct access to all parts of the chip and has greatly eased experimentation. Additionally, we implement some programming chains to control the length of the data-carrying chain.

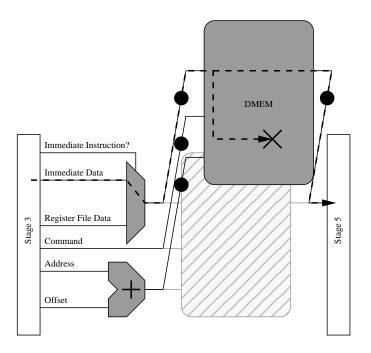

Figure 11 shows a simple schematic of the single-core architecture. The large circles on the buses into and out of the data memory indicate 3D connections. In particular, this schematic highlights the functioning of the three scan chains. First and most important is the *General Scan Chain* (GSC). This chain snakes through each and every flip-flop in the processor core. This chain contains 772 flip-flops per core (12,352 in a sector). This is the chain that is used to load test vectors and return test responses.

To manage the length of the GSC, we implemented two control chains, the *Pipeline*

<sup>&</sup>lt;sup>1</sup>The exception is the power and ground rails. A short anywhere in these networks will fail the chip.

Figure 11. A schematic of the single-core architecture, highlighting the function of the three scan chains.

*Bypass Chain* (PBC) and the *Core Bypass Chain* (CBC). The PBC is used to exclude individual GSC segments within a core. It is composed of nine bits per core, 144 per sector (four are not shown in Figure 11; they correspond to buffers needed to communicate with a core's four neighbors). The CBC is used similarly, but it bypasses an entire core's GSC segments; the CBC contains 16 bits per sector. Note that the GSC has one unbypassable flip-flop on its output. Its purpose is to prevent timing violations; without it, multiple cores could be bypassed and the GSC could run for millimeters without encountering a flip-flop, which would fail the set-up time requirement.

### 3.4.2.3 Central Test Controller

The *Central Test Controller* (CTC) is shown in Figure 12. This unit controls all operation (both functional and test) of 3D-MAPS. Because this test chip lacks traditional off-chip memory interfaces, the CTC serves as the only connection between the processor and the outside world. Modeled after the IEEE 1149.1 test access port, the CTC contains some components that are specific to each sector (and so independent from one another as require for graceful degradation) and some shared components.

Figure 12. A circuit diagram of entire CTC, including per-sector components.

**Sector Hardware** Each sector, as was also shown in Figure 10, is given a pair of I/Os. These pins are the *Test Data In* (TDI) and *Test Data OUT* (TDO) pins respectively, and they function to insert data into the processor and capture data produced by the processor. As shown at the top of Figure 12, the TDI and TDO signals (and all other off-chip signals) must traverse the redundant TSV arrays to access the I/O pads on the backside of the thinned tier. Internal to the CTC, the TDI signals are delayed by four cycles; this synchronizes the arrival of the scan chain signals at the first processor core with the arrival of the global control signals produced by the TCSM, which require four cycles to broadcast. The TDO signals have an attached flip-flop as well; this final flip-flop serves to maximize the timing margin available for the output signal to traverse the package and PCB.

Also internal to the CTC is a fourth scan chain for each sector, the one-bit-long *Sector Control Chains* (SCC). The SCC is the bit that actually disables a bad sector, both closing the sector boundaries and masking its *done* and *barrier* signals. Because it is so short, the SCC also serves as a quick way to test the functionality of the CTC itself.

Figure 13. State diagram for the TCSM. Dashed arrows represent TMS='0' transitions, solid arrows TMS='1' transitions. Bolded states do not change state on TMS='1'. Note that holding TMS='0' will always return the machine to the reset state within three clock cycles. For clarity, output signals are not shown; see Table 2.

**Test Control State Machine** The shared components consist of the TCSM and the *barrier* and *done* logic. The TCSM (Figure 13) is modeled after the IEEE 1149.1 state machine. Effectively, we have merged the command register (specified by the standard) into the TCSM to create a set of hard-coded test modes. As with the IEEE 1149.1 state machine, a single input bit, the *Test Mode Select* (TCSM) signal is used to control the TCSM, and holding this signal low guarantees that the TCSM returns to the initial state. In Figure 13, a bolded state indicates that the TCSM loops in that state when the TMS is high. All other transitions are shown, with a solid arrow indicating the high transition and a dotted arrow indicating the low transition.

The TCSM has six encoded modes: two for test, three for configuration, and one for execution. The *logic test* (Ltest) and *memory test* (Mtest) modes are one- and two-cycle test modes, respectively. Ltest is used to test all logic paths, including the 3D interface (detailed in Section 3.4.3). Mtest is used to both test the memories and to load/unload them at the beginning/end of execution. Two cycles are required because the memories must

| Signal   | Purpose                            | State(s) Active                  |

|----------|------------------------------------|----------------------------------|

| Test_en  | Places entire chip in test mode    | All states except Ltest_capture, |

|          |                                    | Mtest_capture, EXE_run           |

| RF_en    | Allows writes to the register file | Ltest_capture, EXE_run           |

|          |                                    |                                  |

| Mem_en   | Allows writes to the IM and DM     | Mtest_launch, EXE_run            |

|          |                                    |                                  |

| PBC_hold | Freezes the contents of the        | All states except PBC_scan       |

|          | pipeline bypass chain              |                                  |

| CBC_hold | Freezes the contents of the core   | All states except CBC_scan       |

|          | bypass chain                       |                                  |

| SCC_hold | Freezes the contents of the sector | All states except SCC_scan       |

|          | control chain                      |                                  |

Table 2. List of global control signals produced by the TCSM, their functions, and the TCSM states in which they are active.

respond to the input data they receive on the first cycle. The three configuration modes are used to set the contents of the PBC, CBC, and SCC respectively. Finally, the execution mode sets the processor in functional mode and allows programs to execute. The actual execution state is sandwiched between two scan states, which allow execution to be halted and debugged by scanning temporary state out of and then back into the machine.

**TCSM Control Signals** The TCSM produces four critical control signals: *test\_en*,  $rf\_en$ , and *mem\_en*. Test enable puts the chip into serial scan mode for test instead of parallel load mode for program execution. It is disabled only for the scan test, memory capture, and execution states. The register file and memory enable signals are used to protect the state in their respective units during scan cycles. Register file enable is enabled in scan test and execution states only, and memory enable is enabled only in memory launch and execution states. The TCSM produces a further three *hold* signals, one each for the PBC, CBC, and SCC chains, used to hold the contents of these chains once they have been programmed. All signals are summarized in Table 2. Note that these six signals (with the exception of SCC hold) that are broadcast globally and so necessitate the synchronization flip-flops discussed previously.

**Functional Signals** The finally component of the CTC is the reduction logic for the *barrier* and *done* signals. For *done*, the four sector signals are masked according to the SCC chains and ANDed together to produce the final, off-chip signal. Handling *barrier* is slightly more complicated. The final *barrier* signal is calculated and sent off-chip, identical to *done*. However, one last control signal, coming from TDI<0>, is ANDed into the tree before this signal is broadcast out as the barrier acknowledge; the purpose of this is to create breakpoint-style functionality.

When a program produces an erroneous result on an experimental chip like this, it is always a challenge to determine if the problem is in the hardware or the software. As such, we have maximized our program debugging capabilities. As mentioned previously, the execution state in the TCSM is both proceeded and followed by scan states. This allows us to pause the execution, read out the contents of the pipeline stages, reload these same contents back into the pipelines, and resume execution exactly where it left off. Of course, this only works if the exact cycle number of interest is known. For cases where it is not, breakpoint functionality is desired; this is where the off-chip barrier signal comes in (Figure 12, leftmost AND gate).

During normal execution, this signal is held high, and barriers resolve as quickly as possible without any outside interference. However, in debug mode, we can hold this signal low. When the program encounters the barrier, it will not resolve, and we can then read out the memory and register file contents for examination (unfortunately, the pipeline contents will be mostly lost waiting for the barrier signals to reach the CTC initially, but this is unavoidable). After the memory is read out, we set the off-chip barrier signal, and the program resumes execution. Thus, by inserting barriers at key points, we can break the program execution at any point, a very useful debugging feature. Because barriers are reported off-chip, the test system can count barriers as they occur to distinguish between breakpoints and synchronization points, allowing the latter to resolve unimpeded and maintaining full chip functionality even in debug mode.

### 3.4.2.4 Executing a Program

Here we describe the basic process for executing a program (assuming an all-good processor). First, we enable all sectors by setting the SCC. Then we enable all cores for scan by setting CBC appropriately. Third, using PBC, we enable only pipeline stages one and three. Then we loop through the memory load/test branch of the TCSM a few thousand times to fill the IMEM and DMEM. Now that the program is loaded, we enter the *EXE\_init* state. In this state, we scan all zeros into the chip, a state architecturally defined to be safe.<sup>2</sup> We also use this state to ramp the clock up from test frequency to core frequency, if desired.

Next, we enter one final preparation state, which ensures the initial PC is correctly read<sup>3</sup>. Finally, we execute the program. Upon receiving the *done* signal, we return to the memory load/test branch to read out the contents of the memory and verify the output of the program—of course, setting the PBC to pipeline stage three and five only (for sending read commands and receiving read data, respectively) will speed up the read out process. This process is then repeated for each benchmark and data set.

#### 3.4.3 Testing 3D-MAPS

The 3D-MAPS chip has been fabricated, packaged, and mounted to a test system at the Georgia Institute of Technology, School of Electrical and Computer Engineering. We have found significant success applying test patterns with the described test architecture. Numerous bugs have been removed from both the C++ model and the test system RTL. We have even discovered and resolved a couple of discrepancies between the 3D-MAPS RTL and the actual chip. These discrepancies were quite unexpected, since the chip was compiled and implemented via CAD tools directly from the RTL description.

So far, testing has shown that 3D-MAPS has been fabricated exactly as described in our GDSII files; no manufacturing bugs have been found. One design bug has been discovered. In our design methodology, we adopted an active-high standard for enable signals (i.e. a

<sup>&</sup>lt;sup>2</sup>"Safe" means the program state (i.e. IMEM, DMEM, and register file contents) will not change.

<sup>&</sup>lt;sup>3</sup>In normal operation, the PC loads either the previous PC or the branch target incremented by eight. The extra cycle is required to avoid that plus-eight calculation.

Figure 14. A schematic of the path utilized to verify the 3D interface. A shadow of the DMEM is shown on the bottom tier to more clearly show its functional connections to the rest of the processor.

unit is active when its enable signal is a logical one). The memory compiler used to produce the IMEM and DMEM however used active-low enables. In most cases, the conversion from active-high to active-low was properly made. However, one case was missed. It occurred in the logic that controls for a writing a character or word to the DMEM. This has proven to be a very minor bug and requires only that we play some tricks to fill up the DMEM with data. Additionally, this bug discovery informed the design of version two of 3D-MAPS (which is currently with the fab) by helping us identify and fix a related design flaw in that chip. Overall, it was a very beneficial experience.

### 3.4.3.1 Testing the 3D Interconnect

Here we describe the process required to test the 3D interconnect. Figure 14 shows in detail the 3D path. A memory instruction is launched from pipeline stage three. The instruction (composed of data, address, and the memory command) passes through some logic before traversing the 3D, microbump bus and arriving at the memory. The memory unit simultaneously executes the instruction and immediately copies the input data to the

| Configuration                           | Test Vector Application                 | Test Response   |     |

|-----------------------------------------|-----------------------------------------|-----------------|-----|

| TMS 1 1                                 | 1                                       | 1               | 0   |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |                                         | 0               |     |

| TDI<0:3>                                |                                         | 0               |     |

| 0 0 0                                   |                                         | 0               |     |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |                                         | 0               |     |

| o                                       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0 0 0   | 1 0 |

| 0 1111111111100                         | 0 0 0 0 0 0 0 0 0 0 0 0 0               | 0 0 0 0 0 0 0   | 1   |

| 0                                       | 0 0 0 0 0 10 0 10 0                     | 0 0 0 0 0 0 0   | 1   |

| o                                       | 0 0 0 0 0 0 0 10 0                      | 0 0 0 0 0 0 0   | 1   |

| GOLD 0                                  | 0 10 0                                  | 0 0 0 0 0 0 0 0 | 1 0 |

| MASK 0 0 0                              | 0 0 1 1 1 1 1                           |                 | 0   |

Figure 15. The output of a test of the 3D bus as captured by the logic analyzer.

output. This data traverses the 3D interface again, where it is captured by stage five.

The passing of memory data transparently to the output is quite a convenient feature. It enables a simple, quick test of the 3D bus, as traced out by the dashed arrow in Figure 14. To test the 3D bus, we launch data from stage three, allow it to propagate both into the DMEM (as marked by the X) and on to stage five. Without this functionality, we would be forced to execute back-to-back write-and-read pairs or insert additional DFT hardware, neither of which is ideal. This simple feature has proven quite valuable for enabling quick, direct test of the 3D bus.

Figure 15 shows an example test response when the 3D bus is exercised. From top to bottom, this screen capture shows:

- 1. the TMS signal

- 2. the four TDI signals (one per sector)

- 3. the four TDO responses (one per core)

- 4. the golden response (there is only one for this experiment because all sectors received the same input)

- 5. the mask (this stream identifies which bits are known versus which are don't cares)

The experiment begins with the configuration sequence for SCC, CBC, and PBC. The third visible '1' on TMS marks the application of the test vector wherein the 3D bus is being activated. The fourth visible '1' on TMS indicates that scan out of the test response is occurring. A comparison between the TDO streams and the golden response reveals that 3D-MAPS passed the test. There are a few discernible discrepancies, but they match up perfectly with lows in the mask stream and so are not relevant to the test of the 3D bus.

### 3.4.3.2 Other Experiments

We have sampled many other paths within the chip beyond the 3D bus. So far no manufacturing bugs have been discovered. While this is consistent with a mature process like 130nm, it is surprising how robust the 3D process appears to be. Most importantly, the configuration chains have been fully vetted with a number of fully random test patterns that pushes their functionality to the limits. Other paths such as the DMEM, IMEM, register file, ALUs, and bypass networks have only received limited testing. We expect to fully validate the manufacturing quality of these paths as well as our test capabilities improve.

We have also collected some initial results for power consumption. These results suggest that the simulated power numbers are quite reliable (approximately 20% error). They also suggest that the chip is operating stably at 277MHz. More definitive frequency and power results must wait on further development of the test system, as described previously.

# 3.5 Summary

In this chapter, we presented a new DFT architecture for enabling pre-bond test of 3D die. This architecture is based on the generic test wrapper design, which has already been successfully applied to board-level and SOC test. In this case, we treat each tier as a separate test module. Each tier test wrapper is complete with an LTC and boundary registers. These simple test features suffice for most designs; specifically, this design has been used to great effect in the 3D-MAPS test chip. We also presented a few tricks for maximizing the benefit of implementing a product in 3D while maintaining pre-bond testability and for minimizing the cost of pre-bond testability by amortizing the cost of test resources across several different use cases. Our hybrid signal distribution network creates a minimum amount of active wiring post-bond while maintaining complete functionality pre-bond. Our pre-bond probe pad reuse scheme utilizes the pads in a new way post-bond to maximize the benefit of these costly structures. Taken together, this work establishes a strong foundation for designing fully testable 3D integrated processor systems.

# **CHAPTER 4**

# **3D CIRCUIT DESIGN FOR PRE-BOND TEST**

The previous chapter focused on archecture-level partitionings of 3D designs, wherein the units making up the chip architecture are spread across the tiers but each individual is whole and functional. While this is certainly a powerful design option, even more effective 3D designs are possible if we start to partition the units themselves across multiple tiers. This so-called circuit-level partitioning offers the greatest performance benefits but also poses the toughest challenges to designers. In this chapter, we take a look at a couple circuit-partitioned 3D designs and tackle the problem of testing their component pieces pre-bond.

## 4.1 **3D** Circuit Design and Test

Previous work in 3D design has examined different partitioning schemes for key functional units in high-performance microprocessors. These units include caches [66], instruction schedulers [67], arithmetic units [68], and register files [69]. Some of these—the cache designs in particular—involve what is best described as sub-block partitioning. These designs are easily testable using the wrapper-based test strategy discussed in the previous chapter. Others, most notably the port-split register file design, are partitioned at a very fine granularity and seem completely untestable by known techniques.

To cover this range of partitioning options, two designs are selected as representative cases. These are the bit-partitioned Kogge-Stone adder and the port-partitioned register file. The Kogge-Stone adder represents the easiest of the circuit-partitioned cases, using only a few internal 3D vias and mostly resembling an architecture-partitioned design (i.e. most functionality is still intact pre-bond). The port-split register file, on the other hand, makes extensive use of internal 3D vias and heavily divides functionality across tiers, representing a unique and difficult pre-bond test challenge. These two functional units, an adder and

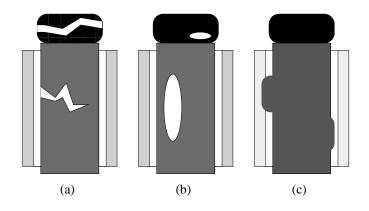

Figure 16. An 8-bit Kogge-Stone adder. (a) shows the planar implementation with its massive wiring area. (b) shows the placement of the 3D vias in the 3D design. (c) shows the true 3D design with the significant wiring reduction.

SRAM memory array, also represent the most commonly seen components inside a microprocessor The particulars of each 3D design and the necessary test strategy are discussed below.

### 4.1.1 Kogge-Stone Adder

The planar and 3D designs of an eight-bit adder are shown in Figure 16. A Kogge-Stone adder makes heavy use of prefix units to minimize the fanout of each unit and increase addition speed. As shown, prefix values are shifted left after each stage by an exponentially increasing distance to produce the carry values. As the bit count increase to 32, 64, and 128 bits, the wiring costs explode. To alleviate this problem, the 3D design proposes a modulus

partitioning of the original operand bits. Figure 16(b) shows a modulus two (i.e., odd and even) partitioning. In the first level of logic, the even bits and odd bits are exchanged across 3D vias. In the last logic level, the generated carries must be shuffled because they are generated on the wrong tier from which they are used. In all other logic levels, the even and odd halves of the adder do not communicate. While the planar implementation had to wire these non-communicative blocks side-by-side, the 3D partitioning enables the independent wiring to get out of each others' way, greatly reducing wiring area. Note that the wiring complexity of the 3D implementation resembles that of a planar 4-bit adder, a significant improvement over the 8-bit planar adder. So modulus two bit-partitioning has the effect of replacing the last, most-complex tract of wiring with a via tract (with wiring complexity equal to the first, simplest wiring tract), significantly increasing addition speed while simultaneously cutting power consumption.

Though only a modulus two partitioning is shown, higher moduli can be used in taller stacks. For example, with four tiers, each group of four bits could be partitioned across the stack. This would replace the two last, most complex wiring tracts with two via tracts of complexity equal only to the first two wiring tracts. Thus the design is very extensible to higher tier counts.

### 4.1.2 Testing the 3D Kogge-Stone Adder

The 3D Kogge-Stone adder has 3D vias only in the first few and last logic levels. Thus, these vias are easily accessible from outside the adder as control points. To test the adder pre-bond, we simply add scan registers at the edge to provide test values on these nets. This enables full structural test of each half of the adder pre-bond.