# Architectural Support for Protecting Memory Integrity and Confidentiality

A Thesis Presented to The Academic Faculty

by

# Weidong Shi

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy Thesis

College of Computing Georgia Institute of Technology August 2006

# Architectural Support for Protecting Memory Integrity and Confidentiality

Approved by:

Dr. Hsien-Hsin Sean Lee School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Mustaque Ahamad College of Computing Georgia Institute of Technology

Dr. Doug Blough School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Gabriel H. Loh College of Computing Georgia Institute of Technology

Dr. Sung Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology

Date Approved: April 19, 2006

To my parents and my wife.

### ACKNOWLEDGEMENTS

I am taking this opportunity to thank individually, all those who have assisted me in one way or the other with my Ph.D Project.

First, I would like to thank my advisor, Dr. Hsien-Hsin Sean Lee, for the support and guidance I received from him. Without his supervision, this work would not have been a reality. In fact, without his willingness to adopt me after I had lost direction in academia, I would have quitted school. I would also like to thank Dr. Mustaque Ahamad, Dr. Doug Blough, Dr. Gabriel H. Loh, and Dr. Sung Kyu Lim for agreeing to be on my thesis committee and reviewing my thesis.

I would also like to extend my gratitude to all the people of the MARS lab for the help given during the various stages of my thesis including Fayez Mohamood, Dong Hyuk Woo, Richard Yoo, Chinnakrishnan Ballapuram. A very special thanks to Mrinmoy Ghosh for editing and commenting my papers multiple times, and Taeweon Suh for providing help on cryptologic synthesis.

I would like to thank Chenghuai Lu, Guofei Gu, and Tao Zhang for the help or suggestions given for shaping or re-shaping some of the ideas that finally lead to this thesis. Specifically, I would also like to thank Dr. Alexandra Boldyreva for her invaluable help and critical comments on many ideas presented in the thesis.

Especially, I thank Dr. Kenneth M. Mackenzie for introducing me to the research of computer architecture and converting me into a disciple of this wonderful world. Thanks are also due to all the professors who have helped or guided me during my time in Georgia Tech including Dr. Karsten Schwan, Dr. Santosh Pande, Dr. Richard M. Fujimoto, and Dr. Wenke Lee.

I also thank all the other professors and students I have done research with or coauthored with during the time of my Georgia Tech presence including Indrani Paul, Dr. Kalyan S. Perumalla, Dr. Josh Fryman, Jun Li, Weiyun Huang, Dr. Youtao Zhang, Dr. Jun Yang, Dr. Trevor N. Mudge, Ashley Thomas, Laura Falk, Xiaotong Zhuang.

Most importantly, I would like to thank a very special person, Yang Lu, for all the family support and tolerance I received during the course of my education. Last, thanks for my German shepherd, Xena for all the fun, laugh, and enjoyment she brought when I was bored by writing the thesis.

# TABLE OF CONTENTS

| DE                 | DIC                     | ATION   | <b>N</b>                                                 | iii    |

|--------------------|-------------------------|---------|----------------------------------------------------------|--------|

| AC                 | KNC                     | OWLE    | DGEMENTS                                                 | iv     |

| LIS                | $\mathbf{T} \mathbf{O}$ | F TAE   | BLES                                                     | x      |

| LIST OF FIGURES xi |                         |         |                                                          |        |

| SUMMARY            |                         |         |                                                          | xiv    |

| Ι                  | INT                     | RODU    | UCTION                                                   | 1      |

|                    | 1.1                     | Thesis  | Organization                                             | 3      |

| II                 | $\operatorname{CH}_4$   | ALLEI   | NGES: MEMORY SECURITY AND SECURE MICRO-PROC              | CESSOR |

|                    | 2.1                     | Applic  | eations                                                  | 4      |

|                    | 2.2                     | Threat  | t Model                                                  | 6      |

|                    | 2.3                     | Relate  | d Work                                                   | 8      |

|                    |                         | 2.3.1   | Smart Cart and Security SOC                              | 8      |

|                    |                         | 2.3.2   | TCPA - Trusted Computing Platform Alliance               | 9      |

|                    |                         | 2.3.3   | Tamper-Proof Platform And Micro-architecture             | 11     |

| III                | BAS                     | SIC EI  | NCRYPTION MODES AND MAC                                  | 14     |

|                    | 3.1                     | Encry   | ption Mode                                               | 16     |

|                    |                         | 3.1.1   | The Electronic Code Block (ECB) Mode                     | 17     |

|                    |                         | 3.1.2   | The Cipher Block Chaining (CBC) Mode                     | 17     |

|                    |                         | 3.1.3   | The Offset Code Block (OCB) Mode                         | 20     |

|                    |                         | 3.1.4   | Counter Mode                                             | 22     |

|                    | 3.2                     | Compa   | arison of Different Memory Decryption Speedup Techniques | 24     |

|                    |                         | 3.2.1   | Sequence number caching                                  | 25     |

|                    |                         | 3.2.2   | Memory Prefetch and Pre-decryption                       | 25     |

|                    | 3.3                     | Integri | ty Verification                                          | 26     |

|                    | 3.4                     | Impler  | nentation                                                | 26     |

|                    |                         | 3.4.1   | Cipher                                                   | 27     |

|                    | 3.5                     | Simula  | tion Framework                                           | 29     |

|              | 3.6 | Performance Comparison of Encryption Modes                                                                       | 30 |  |  |  |  |

|--------------|-----|------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|              | 3.7 | Conclusions                                                                                                      | 33 |  |  |  |  |

| IV           | CO  | COUNTER PREDICTION 34                                                                                            |    |  |  |  |  |

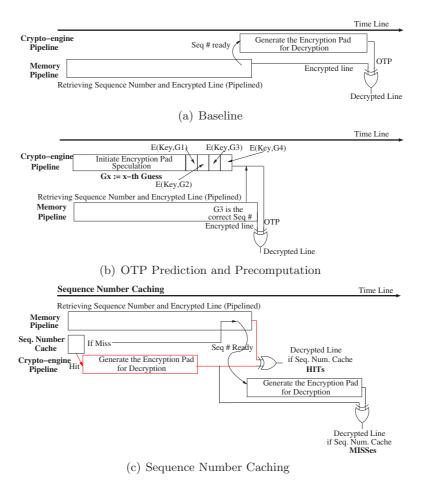

|              | 4.1 | OTP Prediction and Precomputation                                                                                | 34 |  |  |  |  |

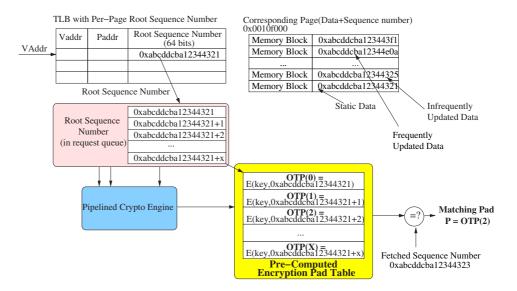

|              |     | 4.1.1 Regular OTP prediction                                                                                     | 35 |  |  |  |  |

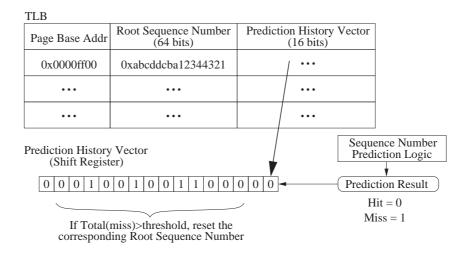

|              |     | 4.1.2 Adaptive OTP prediction for frequently updated data $\ldots$                                               | 38 |  |  |  |  |

|              | 4.2 | Security Analysis                                                                                                | 39 |  |  |  |  |

|              | 4.3 | Simulation Methodology and Implementation                                                                        | 40 |  |  |  |  |

|              |     | 4.3.1 Simulation framework                                                                                       | 40 |  |  |  |  |

|              | 4.4 | Evaluation of adaptive OTP prediction                                                                            | 41 |  |  |  |  |

|              |     | 4.4.1 OTP prediction rate over large execution time                                                              | 41 |  |  |  |  |

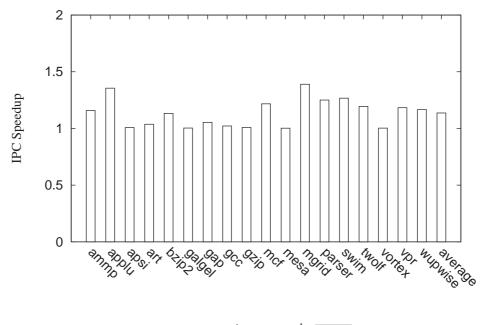

|              |     | 4.4.2 IPC improvement using OTP prediction                                                                       | 43 |  |  |  |  |

|              | 4.5 | Optimizing OTP Prediction                                                                                        | 44 |  |  |  |  |

|              |     | 4.5.1 Profiling misprediction                                                                                    | 44 |  |  |  |  |

|              |     | 4.5.2 Two-level prediction $\ldots \ldots \ldots$ | 46 |  |  |  |  |

|              |     | 4.5.3 Root sequence number history                                                                               | 47 |  |  |  |  |

|              |     | 4.5.4 Context Based Prediction                                                                                   | 47 |  |  |  |  |

|              | 4.6 | Performance Evaluation                                                                                           | 48 |  |  |  |  |

|              | 4.7 | Conclusions                                                                                                      | 52 |  |  |  |  |

| $\mathbf{V}$ | VA  | LUE PREDICTION                                                                                                   | 53 |  |  |  |  |

|              | 5.1 | Value Prediction                                                                                                 | 53 |  |  |  |  |

|              | 5.2 | Ciphertext Speculation                                                                                           | 55 |  |  |  |  |

|              |     | 5.2.1 Triple-DES/DES                                                                                             | 56 |  |  |  |  |

|              |     | 5.2.2 AES                                                                                                        | 56 |  |  |  |  |

|              | 5.3 | MAC Speculation                                                                                                  | 58 |  |  |  |  |

|              | 5.4 | Security Analysis                                                                                                | 59 |  |  |  |  |

|              | 5.5 | Comparison With OTP Prediction                                                                                   | 59 |  |  |  |  |

|              | 5.6 | Simulation Framework                                                                                             | 60 |  |  |  |  |

|              | 5.7 | Performance Analysis                                                                                             | 61 |  |  |  |  |

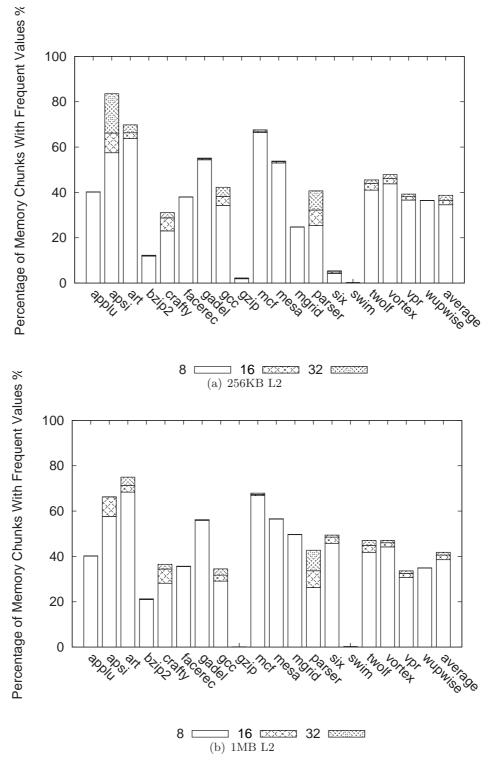

|              |     | 5.7.1 Frequent Values                                                                                            | 61 |  |  |  |  |

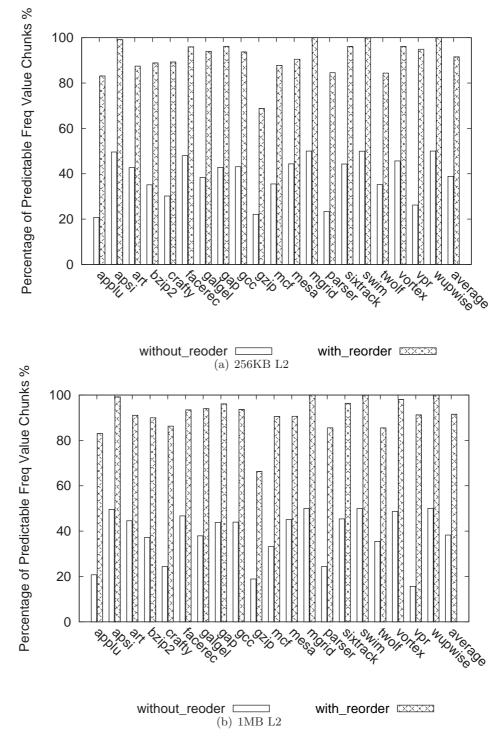

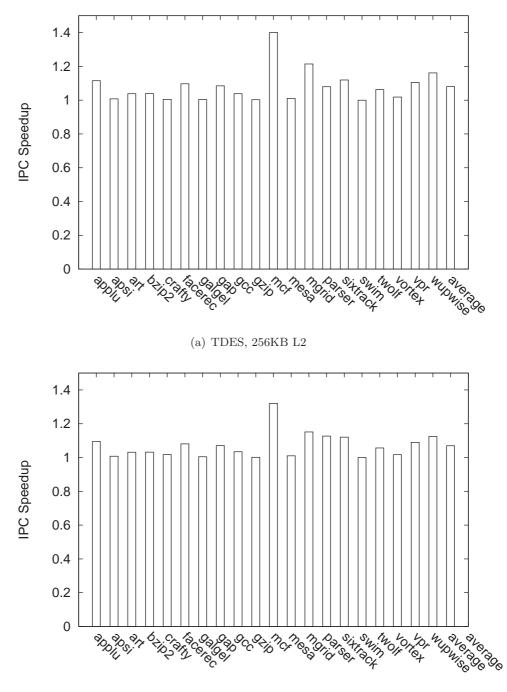

|                       | 5.7.2                                                                                   | Ciphertext and MAC Speculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-----------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                       | 5.7.3                                                                                   | Sensitivity of Memory Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 5.7.4                                                                                   | Number of Frequent Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5.8                   | Concl                                                                                   | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| EFI                   | FICIE                                                                                   | NT MEMORY INTEGRITY VERIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

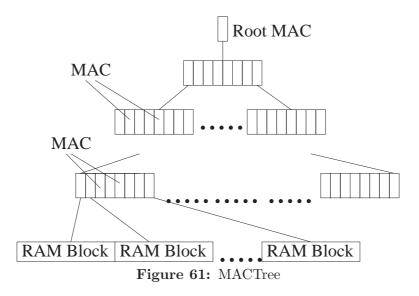

| 6.1                   | MAC                                                                                     | Iree Construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.2                   | Securi                                                                                  | ty Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.3                   | Perfor                                                                                  | mance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 6.3.1                                                                                   | Memory overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 6.3.2                                                                                   | Simulation framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

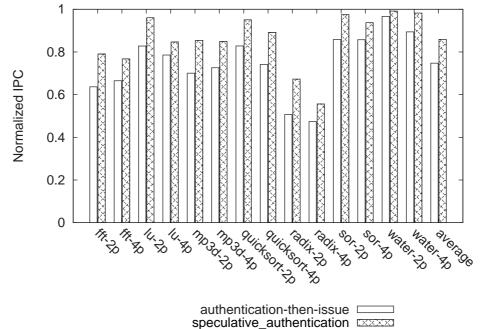

|                       | 6.3.3                                                                                   | Unverified Instruction Speculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 6.3.4                                                                                   | Performance Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.4                   | Concl                                                                                   | usions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| DE                    | COUP                                                                                    | LING INTEGRITY VERIFICATION AND DECRYPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 7.1                   | Memo                                                                                    | bry Fetch as Information Disclosing Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 7.1.1                                                                                   | Threat Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 7.1.2                                                                                   | Exploit Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 7.1.3                                                                                   | Impact of Virtual Memory Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 7.1.4                                                                                   | Effect of Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

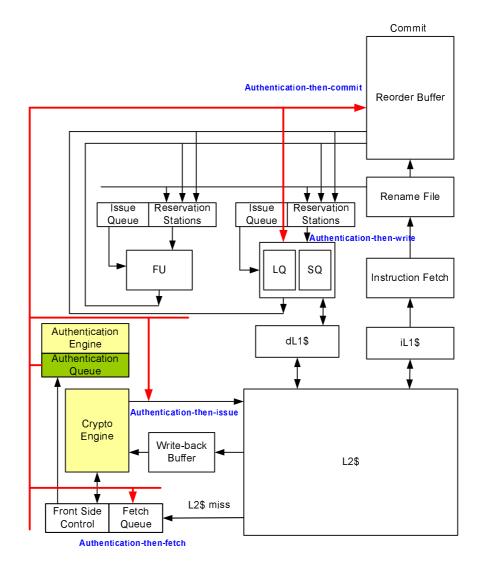

| 7.2                   | Authe                                                                                   | entication Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 7.2.1                                                                                   | Authentication Queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 7.2.2                                                                                   | Authentication Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 7.3                   | Perfor                                                                                  | mance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 7.3.1                                                                                   | Simulation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       | 7.3.2                                                                                   | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

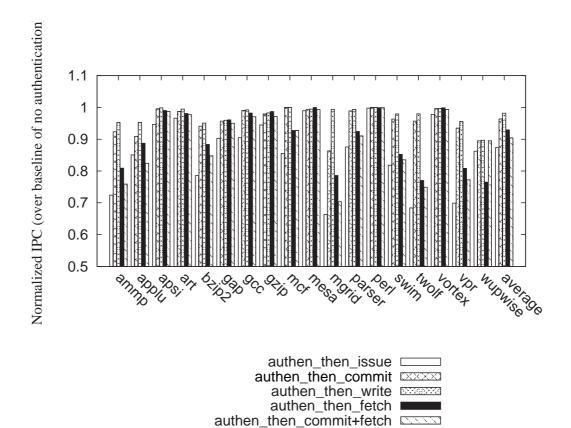

|                       | 7.3.3                                                                                   | Performance Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 7.4                   | Concl                                                                                   | usions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| [ <b>I</b> PR)<br>109 | OTEC                                                                                    | TION OF MEMORY FOR SYMMETRIC MULTI-PROCESSO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 8.1                   | Challe                                                                                  | enges in Shared Memory Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 8.2                   | Securi                                                                                  | ty Model for Shared Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                       | EFI<br>6.1<br>6.2<br>6.3<br>6.4<br>7.1<br>7.2<br>7.2<br>7.3<br>7.4<br>7.4<br>109<br>8.1 | 5.7.3<br>5.7.4<br>5.7.4<br>5.7.4<br>5.7.4<br>5.7.4<br>5.7.4<br>5.7.4<br>5.7.4<br>Conch<br>6.3<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3<br>6.3.4<br>6.3<br>6.3.3<br>6.3.4<br>6.3<br>6.3.3<br>6.3.4<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.1<br>7.1.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.2<br>7.1.3<br>7.1.4<br>7.2<br>7.1.3<br>7.1.4<br>7.2<br>7.1.3<br>7.1.4<br>7.2<br>7.3<br>1<br>7.2.2<br>7.3<br>7.3<br>1<br>7.3.1<br>7.3.2<br>7.3.3<br>7.4<br>Conch<br>7.3.1<br>7.3.2<br>7.3.3<br>7.4<br>Conch<br>7.3.1<br>7.3.2<br>7.3.3 | 5.7.3       Sensitivity of Memory Latency.         5.7.4       Number of Frequent Values         5.8       Conclusion         EFFICIENT MEMORY INTEGRITY VERIFICATION         6.1       MACTree Construction         6.2       Security Analysis         6.3       Performance Analysis         6.3       Performance Analysis         6.3.1       Memory overhead         6.3.2       Simulation framework         6.3.3       Unverified Instruction Speculation         6.3.4       Performance Results         6.4       Conclusions         IDECOUPLING INTEGRITY VERIFICATION AND DECRYPTION         7.1       Memory Fetch as Information Disclosing Channel         7.1.1       Threat Model         7.1.2       Exploit Taxonomy         7.1.3       Impact of Virtual Memory Translation         7.1.4       Effect of Cache         7.2       Authentication Architecture         7.2.1       Authentication Queue         7.2.2       Authentication Architecture         7.3.1       Simulation Framework         7.3.2       Implementation         7.3.3       Performance Result         7.4       Conclusions <td cols<="" td=""></td> |  |

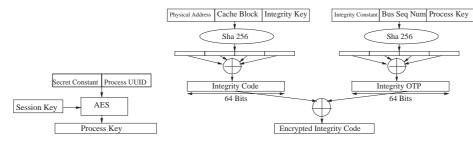

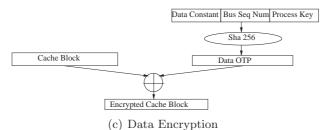

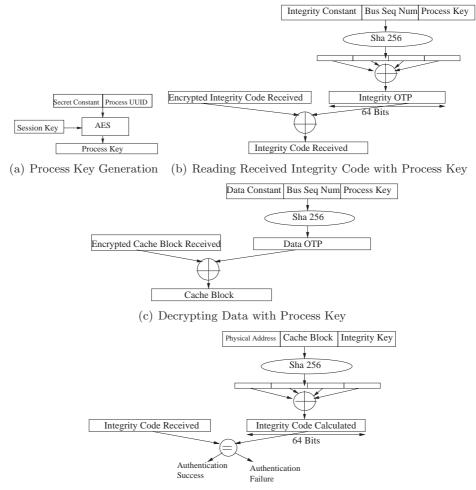

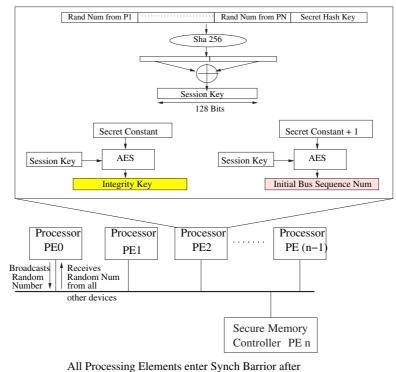

|            | 8.2.1  | Multiprocessor Security Model         | 112 |  |  |

|------------|--------|---------------------------------------|-----|--|--|

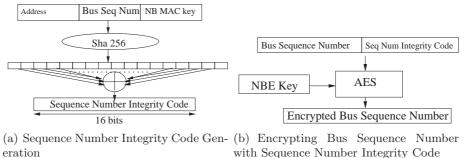

|            | 8.2.2  | Architectural Support of SMP Security | 119 |  |  |

|            | 8.2.3  | Security Analysis                     | 124 |  |  |

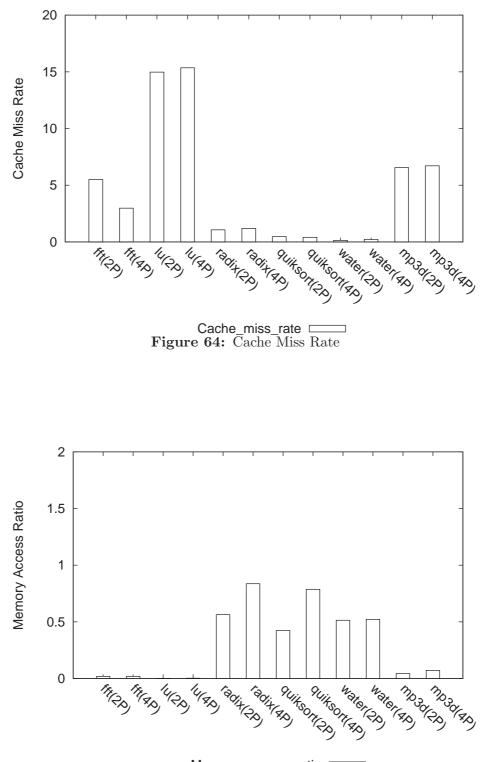

| 8.3        | Perfor | mance Analysis                        | 125 |  |  |

|            | 8.3.1  | Memory overhead                       | 125 |  |  |

|            | 8.3.2  | Simulation Environment                | 125 |  |  |

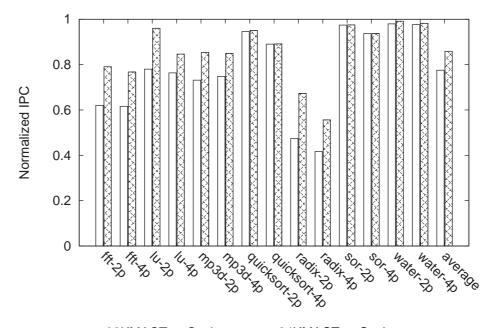

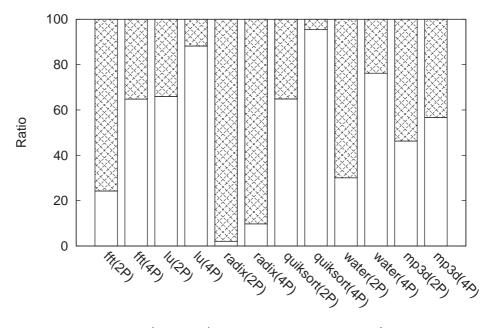

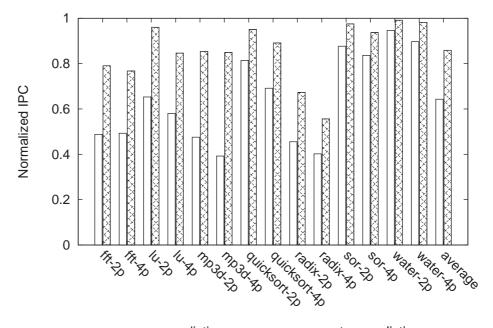

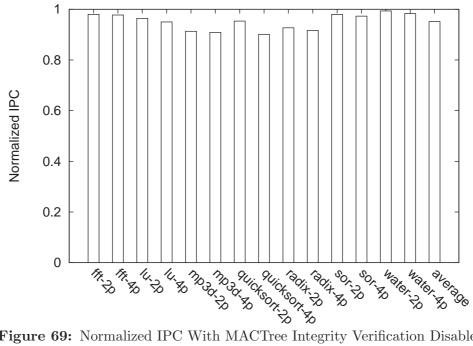

|            | 8.3.3  | Performance                           | 126 |  |  |

| 8.4        | Concl  | usions                                | 132 |  |  |

| IX CO      | NCLU   | SION                                  | 133 |  |  |

| REFERENCES |        |                                       |     |  |  |

# LIST OF TABLES

| 1  | Processor model parameters                                                         | 29  |

|----|------------------------------------------------------------------------------------|-----|

| 2  | Processor model parameters                                                         | 41  |

| 3  | Compare counter prediction with Ciphertext speculation                             | 60  |

| 4  | Processor model parameters                                                         | 60  |

| 5  | Processor Model Parameters                                                         | 76  |

| 6  | Exploit Comparison                                                                 | 91  |

| 7  | Comparison of Security Strength of Different Schemes Against Side-channel Disclose | 96  |

| 8  | Characteristic Comparison of Different Schemes                                     | 97  |

| 9  | Processor model parameters                                                         | 100 |

| 10 | Applications and input parameters                                                  | 126 |

| 11 | Processor model parameters                                                         | 126 |

# LIST OF FIGURES

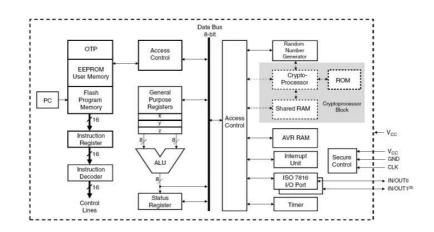

| 1  | Smart Cart Security Chip                                                                                     | 9  |

|----|--------------------------------------------------------------------------------------------------------------|----|

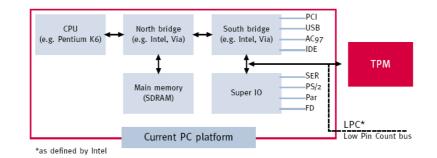

| 2  | TPM and TCPA Platform                                                                                        | 11 |

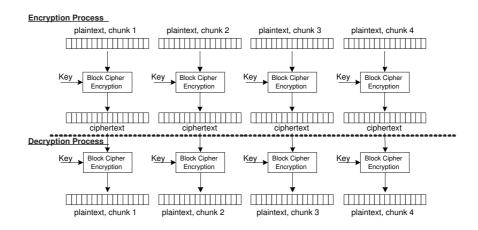

| 3  | Standard ECB mode (electronic code block)                                                                    | 16 |

| 4  | Patterns in ECB Encryption, Courtesy of Wikipedia.com                                                        | 17 |

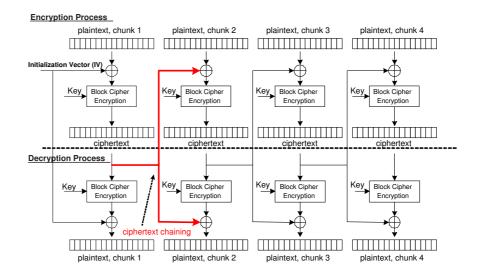

| 5  | Standard CBC mode (cipher block chaining) example $\ldots \ldots \ldots \ldots$                              | 18 |

| 6  | Example showing that second property is not satisfied by CBC Mode                                            | 18 |

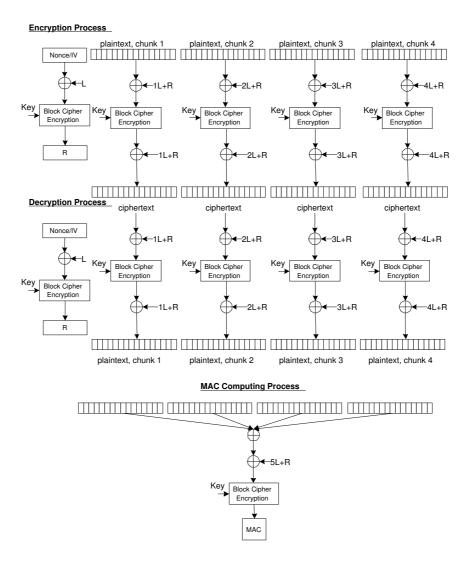

| 7  | OCB Based Protection                                                                                         | 22 |

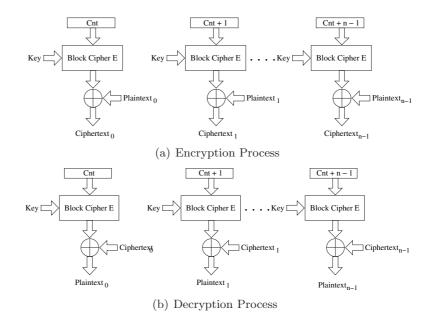

| 8  | Counter Mode Encryption                                                                                      | 23 |

| 9  | Concept of Counter Mode Security                                                                             | 24 |

| 10 | Normalized IPC under CBC or OCB, 256K L2                                                                     | 30 |

| 11 | Normalized IPC under CBC and OCB , 1M L2 $\hdots$                                                            | 31 |

| 12 | Normalized IPC under CBC or OCB, 256K L2                                                                     | 32 |

| 13 | Normalized IPC under CBC and OCB, 1M L2                                                                      | 32 |

| 14 | Timeline Comparison of Different OTP Computation                                                             | 35 |

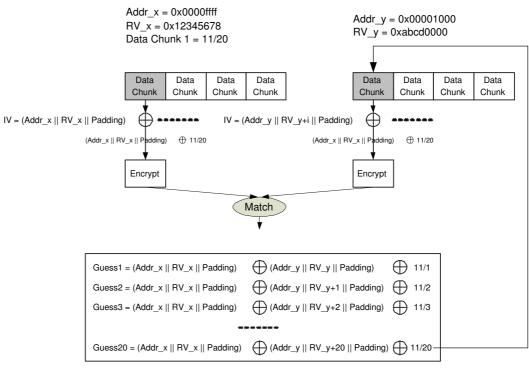

| 15 | OTP Prediction                                                                                               | 37 |

| 16 | Prediction Tracking and Sequence Number Resetting                                                            | 38 |

| 17 | Sequence Number Hit Rates, 256KB L2, 8 billion instructions                                                  | 42 |

| 18 | Sequence Number Hit Rates, 1MB L2, 8 billion instructions $\ldots \ldots \ldots$                             | 43 |

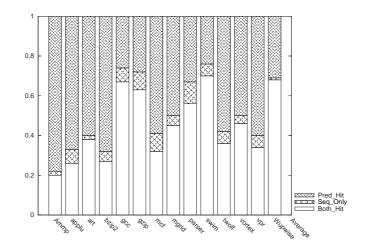

| 19 | Breakdown of Contribution of Sequence Number Cache, and OTP Prediction                                       | 44 |

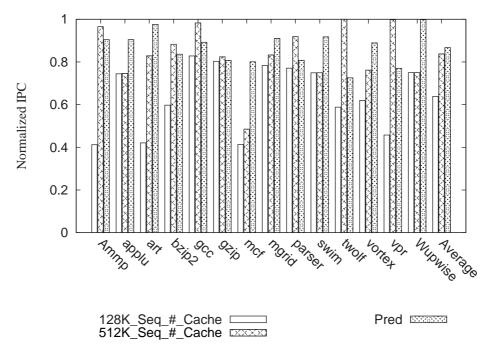

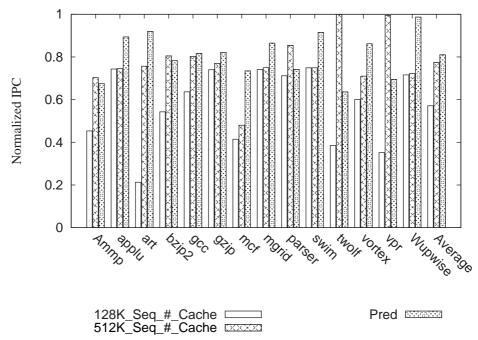

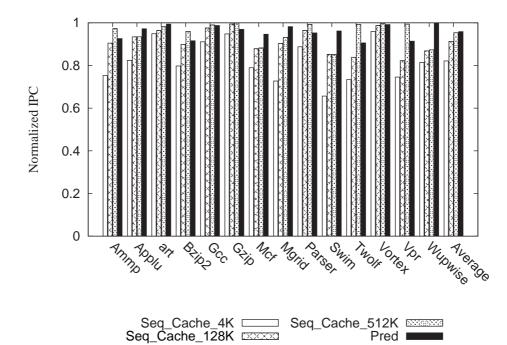

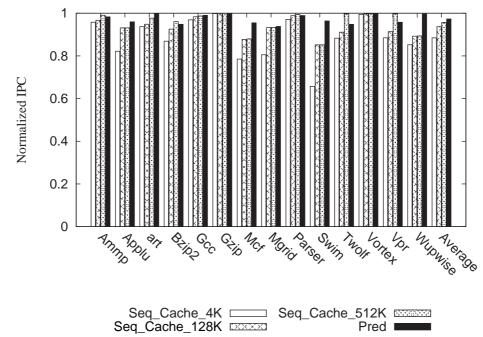

| 20 | Normalized IPC Under Different Sequence Number Cache Sizes(4KB, 128KB and 512KB) vs OTP Prediction, 256KB L2 | 45 |

| 21 | Normalized IPC Under Different Sequence Number Cache Sizes(4KB, 128KB and 512KB) vs OTP Prediction, 1MB L2   | 45 |

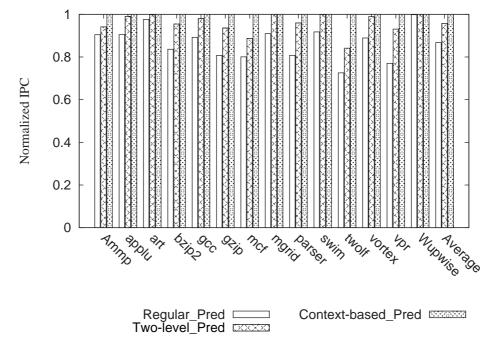

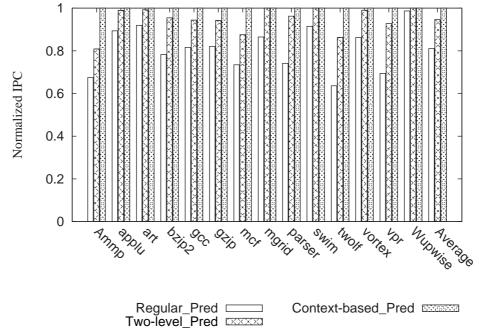

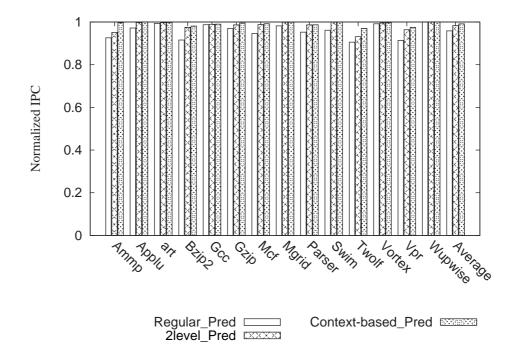

| 22 | Hit Rate of Two-level Pred vs. Context-based Pred vs. Regular Pred, 256KB L2, 8 billion instructions         | 49 |

| 23 | Hit Rate of Two-level Pred vs. Context-based Pred vs. Regular Pred, 1MB L2, 8 billion instructions           | 49 |

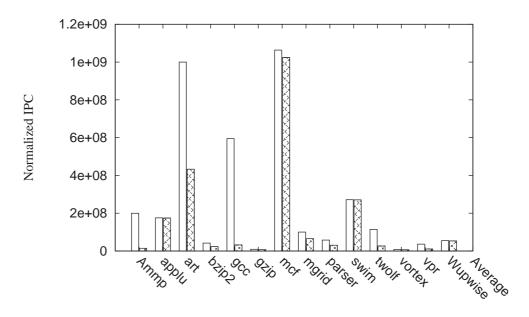

| 24 | Number of Predictions under 256KB vs. 1MB L2                                                                 | 50 |

| 25 | Normalized IPC of Two-level Pred vs. Context-based Pred vs. Regular Pred, 256KB L2                           | 51 |

| 26 | Normalized IPC of Two-level Pred vs. Context-based Pred vs. Regular Pred, 1MB L2                                                                                | 51  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

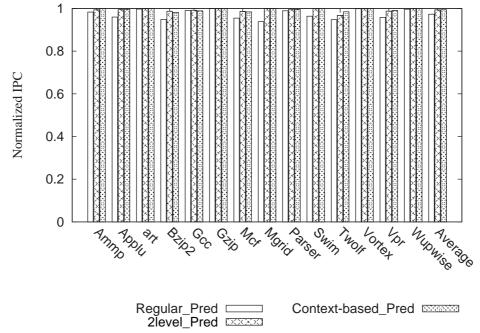

| 27 | Ciphertext Speculation Mechanism                                                                                                                                | 54  |

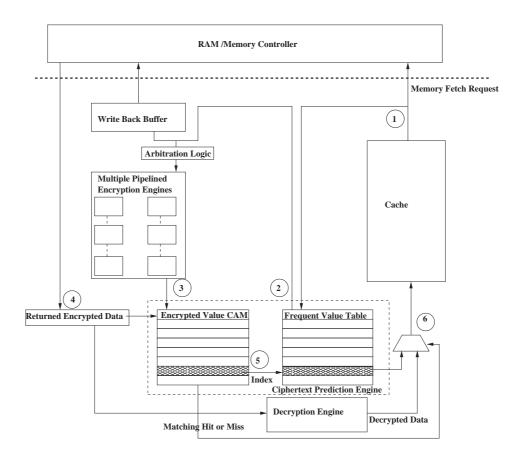

| 28 | Timeline of Ciphertext Speculation                                                                                                                              | 54  |

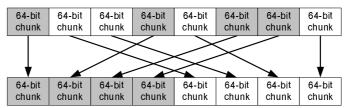

| 29 | Data Chunk Re-ordering                                                                                                                                          | 57  |

| 30 | Percentage of frequent value memory chunks by keeping top 8, 16, 32 64-bit frequent values                                                                      | 62  |

| 31 | Percentage of Predictable Data Chunks Over All Frequent Value Data Chunks<br>Under 128-bit Block Cipher                                                         | 63  |

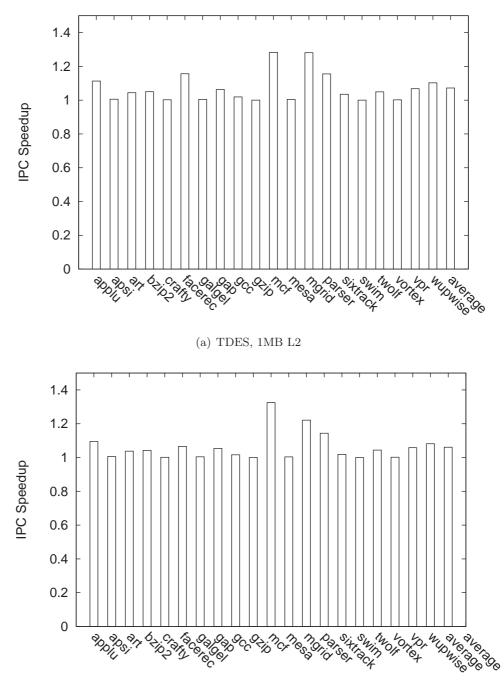

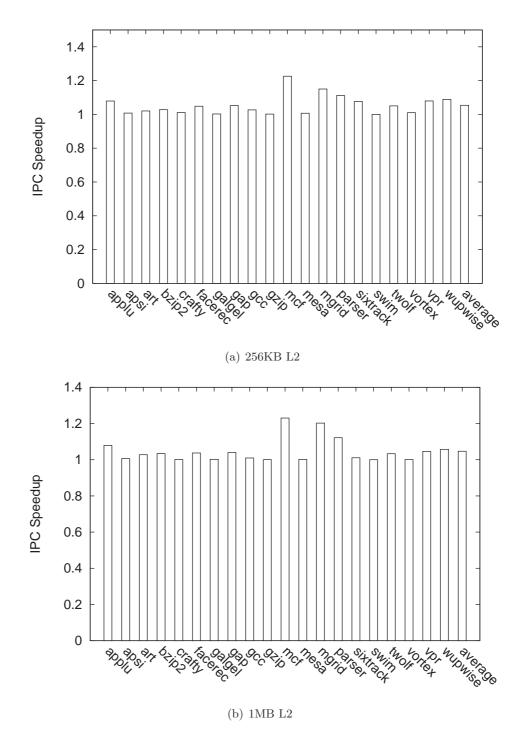

| 32 | IPC Speedup Using Ciphertext and MAC Speculation For Direct Memory<br>Encryption, 256K L2                                                                       | 65  |

| 33 | IPC Speedup Using Ciphertext and MAC Speculation For Direct Memory<br>Encryption, 1M L2                                                                         | 66  |

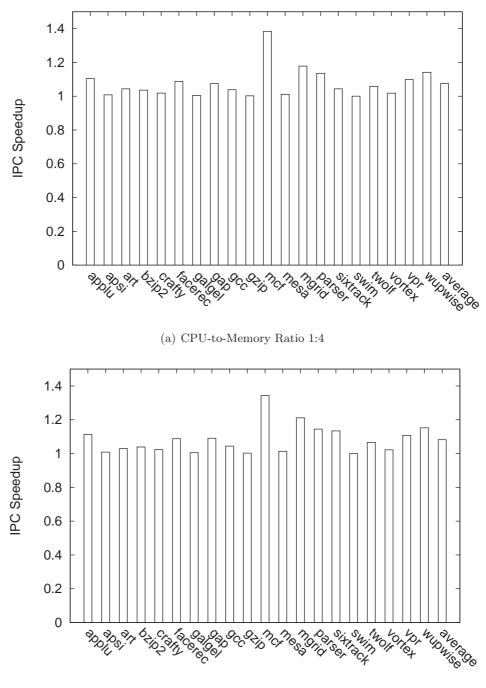

| 34 | IPC Speedup Using Ciphertext and MAC Speculation For Counter Mode) .                                                                                            | 67  |

| 35 | Effect of Memory Speed Relative to CPU Clock Speed, 256KB L2 $\ .$                                                                                              | 69  |

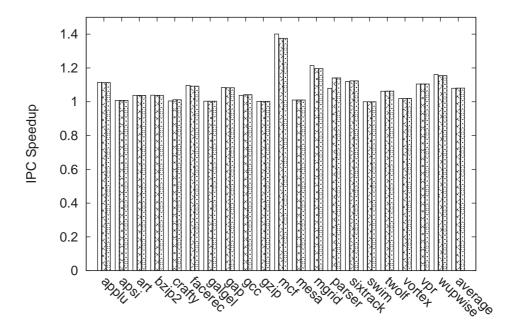

| 36 | Effect of number of guesses/per chunk on performance with TDES encrypted memory, 256K L2                                                                        | 70  |

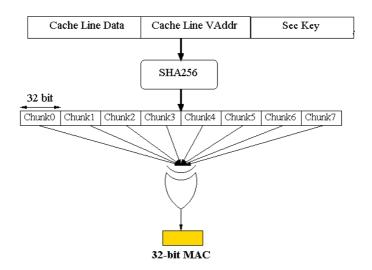

| 37 | 32-bit MAC Generation for a Cache Line                                                                                                                          | 73  |

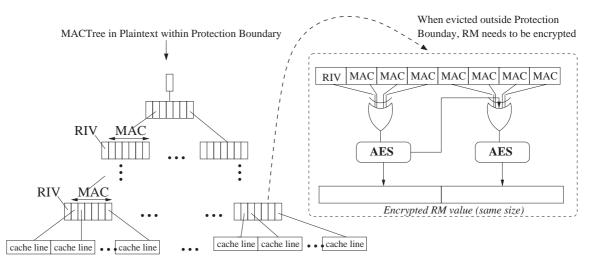

| 38 | Structure of the MACTree in plaintext within protection boundary. Note that a hash value needs to be encrypted when being evicted out of the protection domain. | 73  |

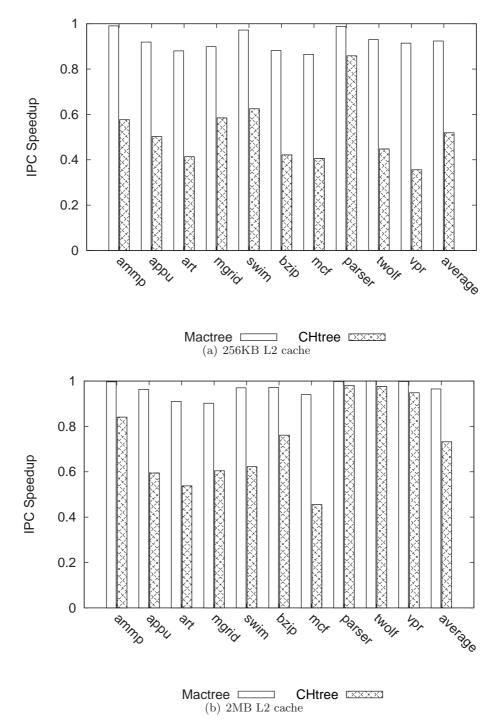

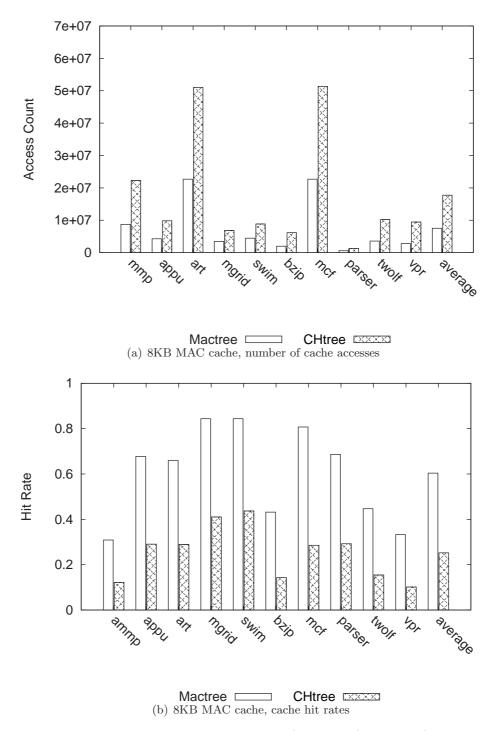

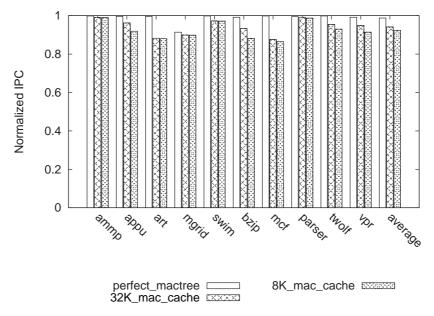

| 39 | Normalized IPC for MACTree and CHTree with 8K MAC cache                                                                                                         | 78  |

| 40 | MAC cache accesses/hit rates (256KB L2)                                                                                                                         | 79  |

| 41 | Performance sensitivity of MAC cache sizes of MACTree (256KB L2)                                                                                                | 80  |

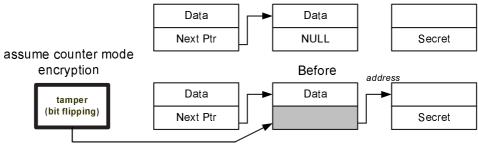

| 42 | Point Conversion Exploit                                                                                                                                        | 87  |

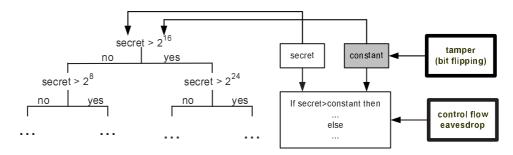

| 43 | Binary Search Tamper                                                                                                                                            | 87  |

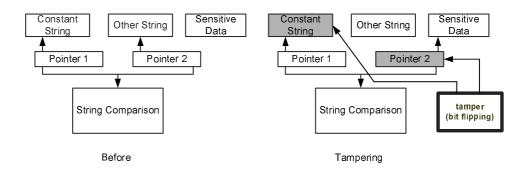

| 44 | Binary Search Exploit Based on String Comparison                                                                                                                | 88  |

| 45 | Alpha Instruction Format                                                                                                                                        | 90  |

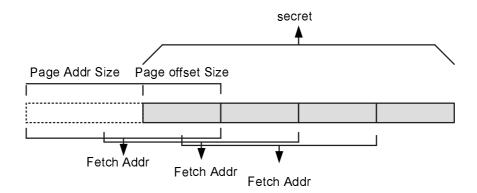

| 46 | Shift Window                                                                                                                                                    | 92  |

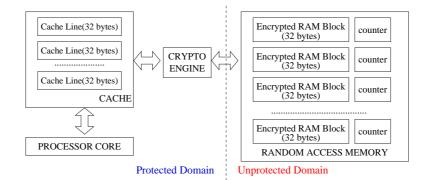

| 47 | Secure Processor Block Diagram                                                                                                                                  | 95  |

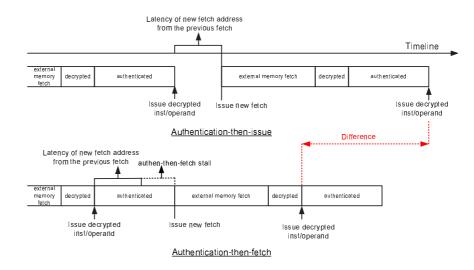

| 48 | Timeline of Authentication-then-fetch vs. Authentication-then-issue                                                                                             | 98  |

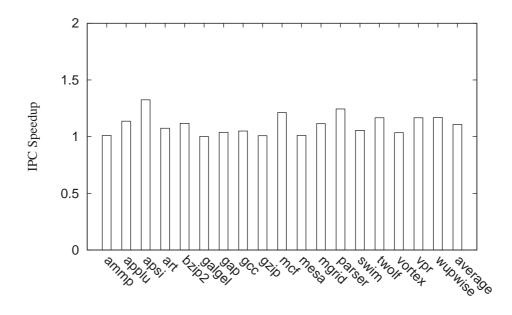

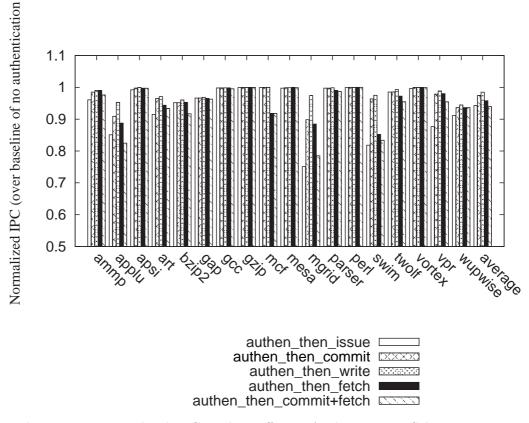

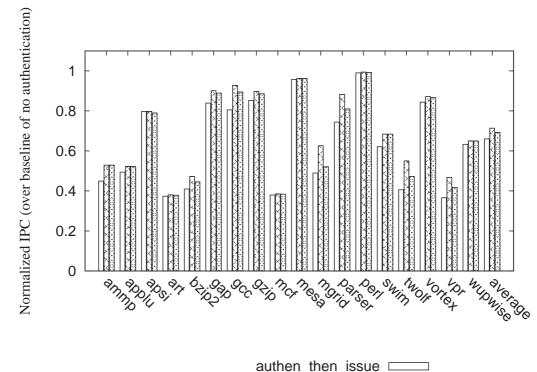

| 49 | Normalized IPC Under Different Authentication Schemes, 256K L2                                                                                                  | 102 |

| 50 | Normalized IPC Under Different Authentication Schemes, 1M L2                                                                                                    | 102 |

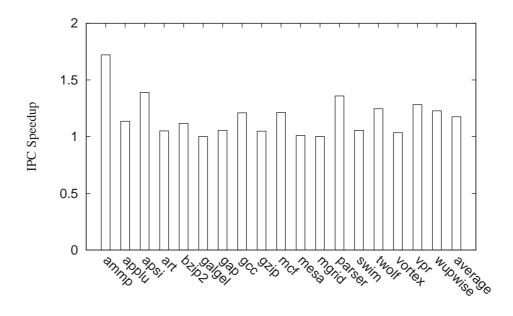

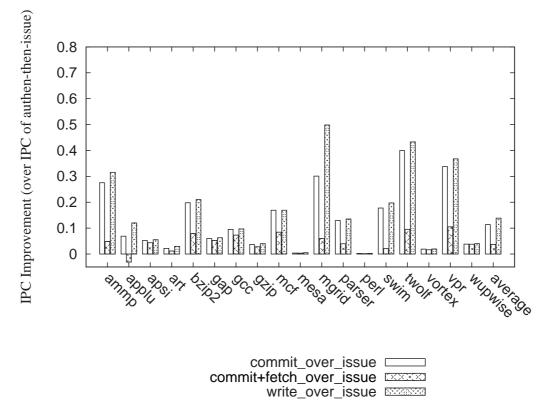

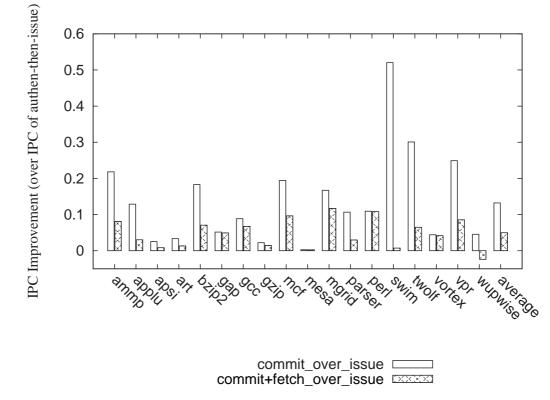

| 51 | Comparison of IPC Speedup Over Authentication-then-issue Using Three Other Schemes, 256K L2                               | 103 |

|----|---------------------------------------------------------------------------------------------------------------------------|-----|

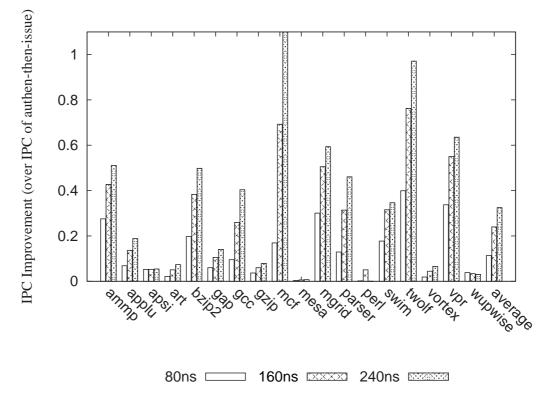

| 52 | IPC Speedup of Authentication-then-commit Over Authentication-then-issue<br>Under Three Authentication Latencies, 256K L2 | 104 |

| 53 | Normalized IPC Under Different Authentication Schemes, 256K L2, 64-Entry RUU                                              | 105 |

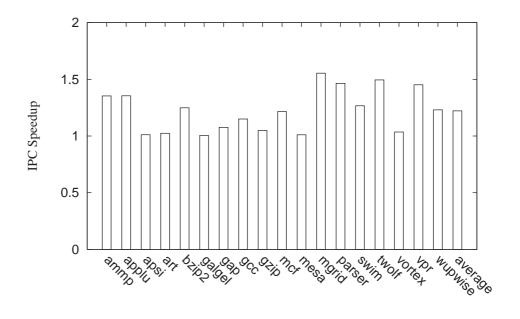

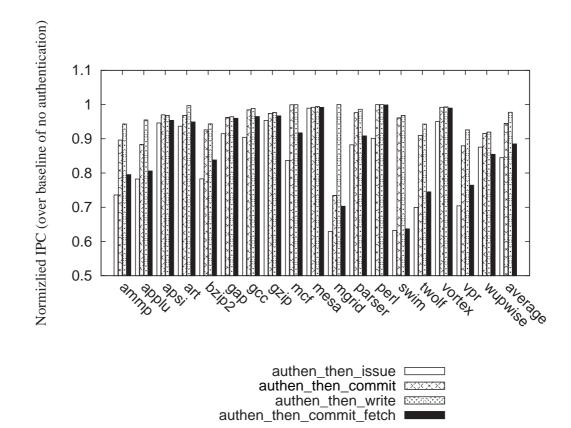

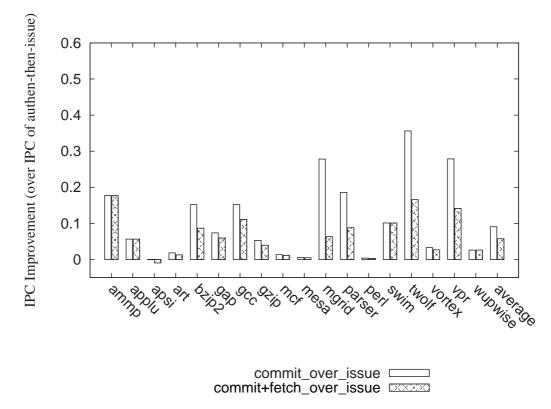

| 54 | Comparison of IPC Speedup Over Authentication-then-issue Under Different<br>Authentication Schemes, 256K L2               | 105 |

| 55 | Normalized IPC Under Different Authentication Schemes, Memory Authen-<br>tication Tree                                    | 106 |

| 56 | Comparison of IPC Speedup Over Authentication-then-issue, Memory Au-<br>thentication Tree                                 | 107 |

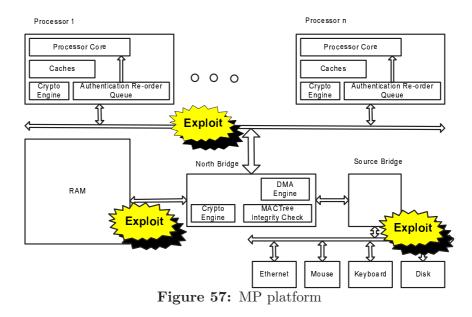

| 57 | MP platform                                                                                                               | 111 |