# DESIGNING HETEROGENEOUS MANY-CORE PROCESSORS TO PROVIDE HIGH PERFORMANCE UNDER LIMITED CHIP POWER BUDGET

A Thesis Presented to The Academic Faculty

by

Dong Hyuk Woo

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Electrical and Computer Engineering

> Georgia Institute of Technology December 2010

# DESIGNING HETEROGENEOUS MANY-CORE PROCESSORS TO PROVIDE HIGH PERFORMANCE UNDER LIMITED CHIP POWER BUDGET

Approved by:

Dr. Hsien-Hsin S. Lee, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sudhakar Yalamanchili School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Marilyn Wolf School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Sung Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Milos Prvulovic School of Computer Science Georgia Institute of Technology

Date Approved: 23 September 2010

To my family.

### ACKNOWLEDGEMENTS

I would like to take this opportunity to thank all those who directly or indirectly helped me in completing my Ph.D. study.

First of all, I would like to thank my advisor, Dr. Hsien-Hsin S. Lee, who continuously motivated me, patiently listened to me, and often challenged me with critical feedback. I would also like to thank Dr. Sudhakar Yalamanchili, Dr. Marilyn Wolf, Dr. Sung Kyu Lim, and Dr. Milos Prvulovic for volunteering to serve in my committee and reviewing my thesis.

I would also like to thank all the MARS lab members, Dr. Weidong Shi, Dr. Taeweon Suh, Dr. Chinnakrishnan Ballapuram, Dr. Mrinmoy Ghosh, Fayez Mohamood, Richard Yoo, Dean Lewis, Eric Fontaine, Ahmad Sharif, Pratik Marolia, Vikas Vasisht, Nak Hee Seong, Sungkap Yeo, Jen-Cheng Huang, Abilash Sekar, Manoj Athreya, Ali Benquassmi, Tzu-Wei Lin, Mohammad Hossain, Andrei Bersatti, and and Jae Woong Sim. A special thanks to Mrinmoy Ghosh for his help in my early research, from which I was able to easily learn how to conduct academic research. Another special thanks to Nak Hee Seong for his help in my recent projects. Countless rounds of in-depth discussion with him helped me to better understand various design trade-offs of memory hierarchy.

On the other hand, I would like to express gratitude to all the people who actively participated in our weekly computer architecture meeting, *arch-beer:* Dr. Gabriel Loh, Dr. Hyesoon Kim, Dr. Nathan Clark, Dr. Samantika Subramaniam, and Dr. Guru Venkataramani, just to name a few. From the heated discussion with them, I learned how to find a new problem, how to develop a reasonable solution to a problem, and how to evaluate a proposed solution fairly. I also appreciate Dr. Josh Fryman and Dr. Allan Knies of Intel Corporation for providing assistance and guidance during the summer internship in 2006. This internship project has later become a part of my thesis. Especially, Dr. Fryman taught me how to read a paper critically, which helped me a lot throughout my graduate study.

Furthermore, I would like to thank all members of our 3D-MAPS project, Krit Athikulwongse, Rohan Goel, Michael Healy, Mohammad Hossain, Moongon Jung, Dae Hyun Kim, Young-Joon Lee, Dean Lewis, Tzu-Wei Lin, Chang Liu, Brian Ouellette, Mohit Pathak, Hemant Sane, Guanhao Shen, and Xin Zhao. While designing a 3D-stacked many-core processor together for this project, they directly and indirectly helped me in many aspects.

In addition to those who I know personally, I would also like to thank anonymous conference and journal reviewers who volunteered to read my papers and provided many useful comments. Additionally, I would like to appreciate those who has developed and maintained the open-source SESC simulator, which was extremely useful throughout my graduate study.

Most importantly, I would like to appreciate my wife, Jung In Sung, for her devotion and endurance. Without her endless support, this thesis would not have been possible. I also thank my son, Nolan Hyunjae Woo, whose smile always cheers me up. Finally, I appreciate my parents, Sang Kyu Woo and Young Hee Shin, for their unconditional love and support not only during my graduate study but also throughout my life so far.

# TABLE OF CONTENTS

| DED  | ICAT             | TION .  |                                              | iii  |  |  |  |  |

|------|------------------|---------|----------------------------------------------|------|--|--|--|--|

| ACK  | ACKNOWLEDGEMENTS |         |                                              |      |  |  |  |  |

| LIST | OF               | TABLE   | 2S                                           | х    |  |  |  |  |

| LIST | OF               | FIGUR   | ES                                           | xi   |  |  |  |  |

| SUM  | MAR              | Υ       |                                              | xiii |  |  |  |  |

| Ι    | INT              | RODU    | CTION                                        | 1    |  |  |  |  |

| II   | ORI              | GIN AI  | ND HISTORY OF THE PROBLEM                    | 4    |  |  |  |  |

|      | 2.1              | Amdal   | hl's Law                                     | 4    |  |  |  |  |

|      | 2.2              | Massiv  | vely Parallel Processors                     | 4    |  |  |  |  |

|      | 2.3              | Tiled . | Architecture                                 | 6    |  |  |  |  |

|      | 2.4              | Accele  | rator Architecture                           | 6    |  |  |  |  |

|      | 2.5              | Snap-0  | On 3D Stacked Layers                         | 7    |  |  |  |  |

|      | 2.6              | Softwa  | re Caching                                   | 7    |  |  |  |  |

|      | 2.7              | Shared  | l Cache Management                           | 8    |  |  |  |  |

|      | 2.8              | Non-U   | niform Cache Architecture                    | 8    |  |  |  |  |

|      | 2.9              | Prefet  | ching Techniques                             | 8    |  |  |  |  |

| III  |                  |         | NG AMDAHL'S LAW FOR ENERGY-EFFICIENT COMPUT- |      |  |  |  |  |

|      | ING              |         | E MANY-CORE ERA                              | 10   |  |  |  |  |

|      | 3.1              | Many-   | Core Design Styles                           | 11   |  |  |  |  |

|      | 3.2              | Augme   | enting Amdahl's Law                          | 12   |  |  |  |  |

|      |                  | 3.2.1   | Models for $P^*$                             | 12   |  |  |  |  |

|      |                  | 3.2.2   | Models for $c^*$                             | 14   |  |  |  |  |

|      |                  | 3.2.3   | Models for $P+c^*$                           | 15   |  |  |  |  |

|      |                  | 3.2.4   | Power-Equivalent Models                      | 16   |  |  |  |  |

|      | 3.3              | Evalua  | ation                                        | 18   |  |  |  |  |

|      |                  | 3.3.1   | Evaluation of a $P^*$                        | 18   |  |  |  |  |

|    |      | 3.3.2   | Evaluation of a $c^*$                                        | 19 |

|----|------|---------|--------------------------------------------------------------|----|

|    |      | 3.3.3   | Evaluation of a $P+c^*$                                      | 21 |

|    |      | 3.3.4   | Evaluation of Power-Equivalent Models                        | 22 |

|    | 3.4  | Summa   | ary                                                          | 24 |

| IV | A 3I | )-INTE  | GRATED BROAD-PURPOSE ACCELERATION LAYER .                    | 25 |

|    | 4.1  | POD A   | Architecture                                                 | 26 |

|    | 4.2  | Hetero  | geneous ISA                                                  | 27 |

|    | 4.3  | Wire-I  | Delay-Aware Design                                           | 30 |

|    | 4.4  | Energy  | r-Efficient Interconnection Network                          | 32 |

|    | 4.5  | Virtua  | l Address Support                                            | 34 |

|    | 4.6  | Minim   | al ISA Modification in the Host Processor                    | 35 |

|    | 4.7  | POD V   | Virtualization                                               | 35 |

|    | 4.8  | Physic  | al Design Evaluation                                         | 36 |

|    | 4.9  | Perform | nance Evaluation                                             | 38 |

|    | 4.10 | Summa   | ary                                                          | 45 |

| V  | CHA  | MELE    | ON ARCHITECTURE                                              | 46 |

|    | 5.1  | C-Mod   | le: Virtualizing Idle Cores for Caching                      | 47 |

|    |      | 5.1.1   | Design for Way-Level Parallelism                             | 50 |

|    |      | 5.1.2   | Design for Way- and Subblock-level Parallelism               | 52 |

|    |      | 5.1.3   | Decoupled Design                                             | 54 |

|    |      | 5.1.4   | NUCA Cache Design                                            | 56 |

|    | 5.2  | P-Mod   | e: Virtualizing Idle Cores as a Prefetcher                   | 63 |

|    |      | 5.2.1   | Virtualized Markov Prefetcher                                | 64 |

|    | 5.3  | Hybrid  | CP-Mode: Virtualizing Idle Cores for Caching and Prefetching | 67 |

|    | 5.4  | Adapti  | veCP-Mode: Mode Adaptation in Chameleon                      | 68 |

|    | 5.5  | Experi  | mental Results                                               | 69 |

|    |      | 5.5.1   | Simulation Environment                                       | 69 |

|    |      | 5.5.2   | Evaluation of C-Mode                                         | 71 |

|    |     | 5.5.3   | Evaluation of P-Mode                                          | 75  |

|----|-----|---------|---------------------------------------------------------------|-----|

|    |     | 5.5.4   | Evaluation of Hybrid<br>CP-Mode and Adaptive<br>CP-Mode $\ .$ | 76  |

|    |     | 5.5.5   | Hardware and Power Overhead                                   | 79  |

|    | 5.6 | Summ    | ary                                                           | 81  |

| VI | CON | MPASS:  | COMPUTE SHADER ASSISTED PREFETCHING                           | 83  |

|    | 6.1 | Introd  | uction                                                        | 83  |

|    | 6.2 | Baseli  | ne GPU Architecture                                           | 84  |

|    | 6.3 | COMI    | PASS                                                          | 89  |

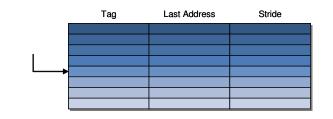

|    |     | 6.3.1   | Miss Address Provider                                         | 90  |

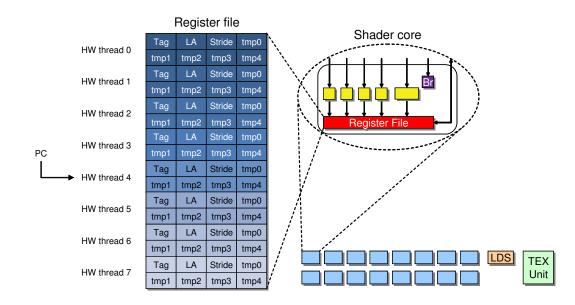

|    |     | 6.3.2   | Threads and Register Files                                    | 91  |

|    |     | 6.3.3   | An Example of a COMPASS Shader                                | 93  |

|    |     | 6.3.4   | A Prefetch Instruction                                        | 94  |

|    |     | 6.3.5   | Usage Model                                                   | 94  |

|    | 6.4 | Differe | ent COMPASS Shader Designs                                    | 95  |

|    |     | 6.4.1   | Stride COMPASS                                                | 96  |

|    |     | 6.4.2   | Markov COMPASS                                                | 97  |

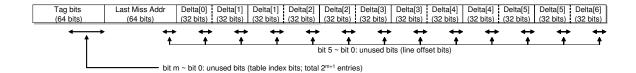

|    |     | 6.4.3   | Delta COMPASS                                                 | 98  |

|    |     | 6.4.4   | A Simplified Region Prefetcher                                | 100 |

|    |     | 6.4.5   | Custom COMPASS Design for 429.mcf                             | 101 |

|    | 6.5 | Exper   | imental Results                                               | 102 |

|    |     | 6.5.1   | Simulation Framework                                          | 102 |

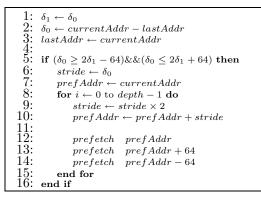

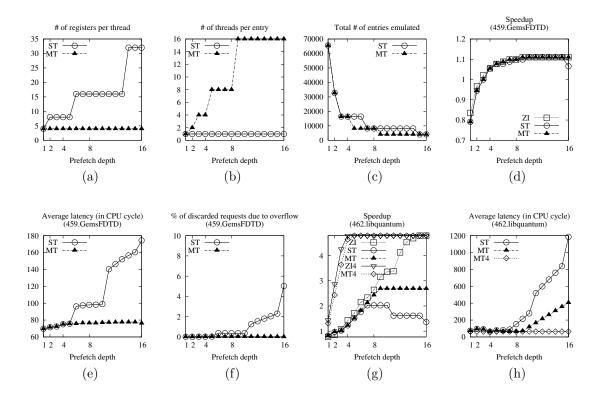

|    |     | 6.5.2   | Evaluation of Stride COMPASS                                  | 104 |

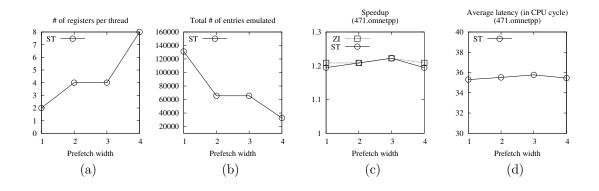

|    |     | 6.5.3   | Evaluation of Markov COMPASS                                  | 107 |

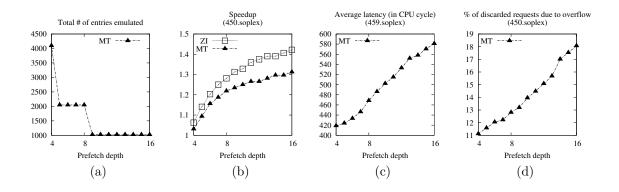

|    |     | 6.5.4   | Evaluation of Delta COMPASS                                   | 108 |

|    |     | 6.5.5   | Evaluation of Region COMPASS                                  | 109 |

|    |     | 6.5.6   | Evaluation of Custom COMPASS                                  | 110 |

|    |     | 6.5.7   | COMPASS vs. GHB Stride Prefetchers                            | 110 |

|    |     | 6.5.8   | Multicore Effects                                             | 112 |

|     |      | 6.5.9  | Hare | dwar | e, So | oftwa | are, | and | Pow | er O | verh | ead | <br> | <br> | 114 |

|-----|------|--------|------|------|-------|-------|------|-----|-----|------|------|-----|------|------|-----|

|     | 6.6  | Summ   | ary  |      |       | •••   |      |     |     | • •  |      |     | <br> | <br> | 119 |

| VII | CON  | ICLUS  | ION  |      |       | •••   |      |     |     |      |      |     | <br> | <br> | 121 |

| REF | EREI | NCES . |      |      |       |       |      |     |     |      |      |     | <br> | <br> | 124 |

# LIST OF TABLES

| 1  | POD benchmark.                                                                   | 38  |

|----|----------------------------------------------------------------------------------|-----|

| 2  | Host processor configuration.                                                    | 70  |

| 3  | Latency and throughput of different C-mode designs                               | 71  |

| 4  | Latency and throughput of different P-mode designs                               | 75  |

| 5  | A modified delta prefetch address calculation algorithm (miss address $= 1024$ ) | 100 |

| 6  | A sample stride pattern of $429.mcf$ (cache line size: 64B)                      | 102 |

| 7  | Platform configurations.                                                         | 103 |

| 8  | Overall results (d: prefetch depth, w: prefetch width)                           | 111 |

| 9  | Dual-core simulation results                                                     | 112 |

| 10 | GPU utilization.                                                                 | 116 |

| 11 | GPU average power.                                                               | 116 |

| 12 | GPU energy consumption                                                           | 117 |

| 13 | Off-chip bus energy consumption                                                  | 117 |

| 14 | CPU and L2 cache energy consumption.                                             | 118 |

| 15 | CPU, GPU, L2 cache, and off-chip bus energy consumption                          | 118 |

| 16 | CPU, GPU, L2 cache, and off-chip bus energy efficiency (normalized perf/joule).  | 119 |

# LIST OF FIGURES

| 1  | Many-core design styles                                                                                                           | 11 |

|----|-----------------------------------------------------------------------------------------------------------------------------------|----|

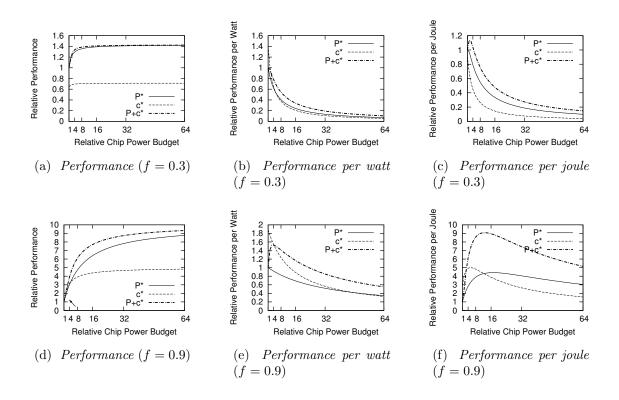

| 2  | Performance, performance per watt, and performance per joule of a $P^*$ $(k = 0.3)$ .                                             | 19 |

| 3  | Performance, performance per watt, and performance per joule of a $c^*$ $(s_c = 0.5, w_c = 0.25, \text{ and } k_c = 0.2)$ .       | 20 |

| 4  | Performance, performance per watt, and performance per joule of a $P+c^*$ ( $k = 0.3, s_c = 0.5, w_c = 0.25$ , and $k_c = 0.2$ ). | 21 |

| 5  | Power-equivalent models $(k = 0.3, s_c = 0.5, w_c = 0.25, and k_c = 0.2)$ .                                                       | 22 |

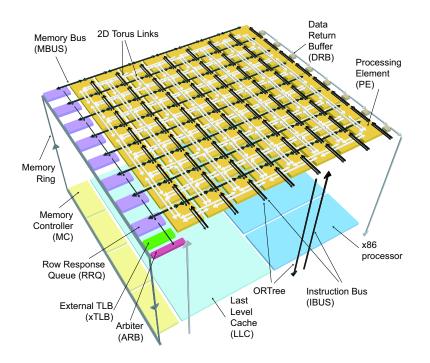

| 6  | POD architecture in stacked die arrangement.                                                                                      | 26 |

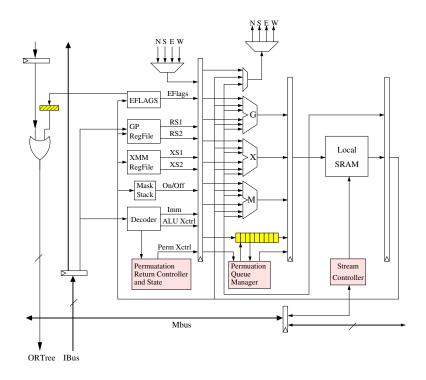

| 7  | A processing element tile.                                                                                                        | 27 |

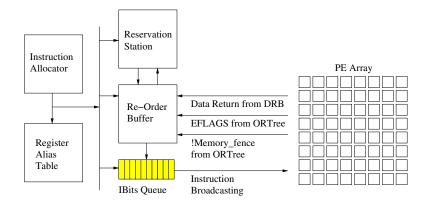

| 8  | IBits queue in the superscalar pipeline                                                                                           | 29 |

| 9  | One detailed POD column                                                                                                           | 31 |

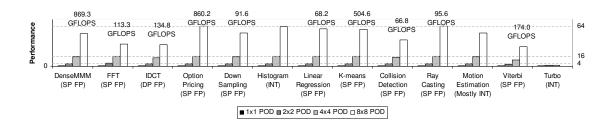

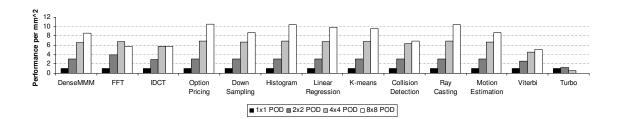

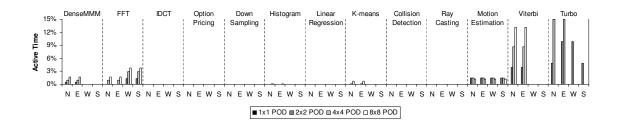

| 10 | Relative performance (normalized to $1 \times 1$ POD)                                                                             | 40 |

| 11 | Extrinsic LLR algorithm [94].                                                                                                     | 41 |

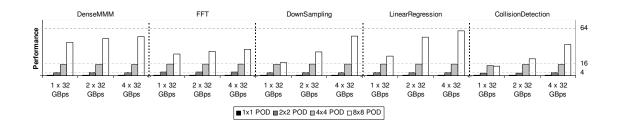

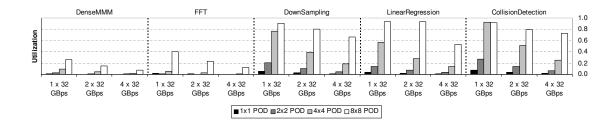

| 12 | Effect of off-chip memory bandwidth                                                                                               | 42 |

| 13 | Relative performance per mm <sup>2</sup> (normalized to $1 \times 1$ POD)                                                         | 43 |

| 14 | Relative performance per joule (normalized to $1 \times 1$ POD)                                                                   | 44 |

| 15 | 2D torus network active time                                                                                                      | 45 |

| 16 | Chameleon Virtualizer (not scaled)                                                                                                | 48 |

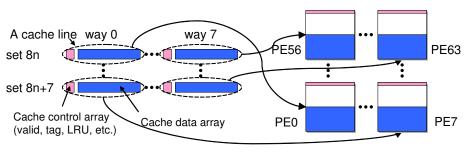

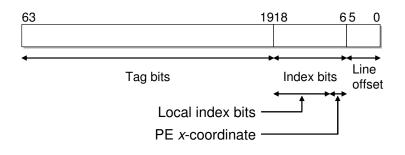

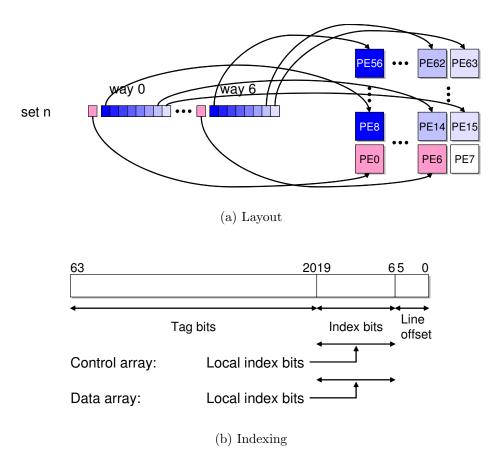

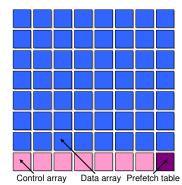

| 17 | Way-level parallelism (8-way 4MB cache).                                                                                          | 50 |

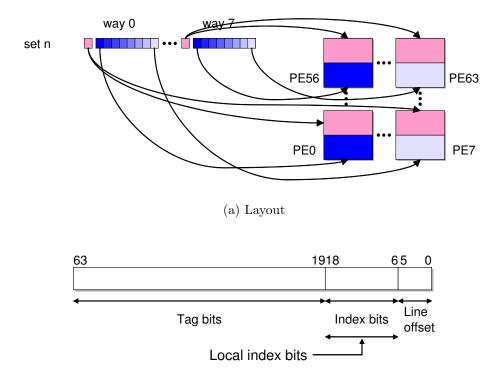

| 18 | Way- and subblock-level parallelism (8-way 4MB cache)                                                                             | 52 |

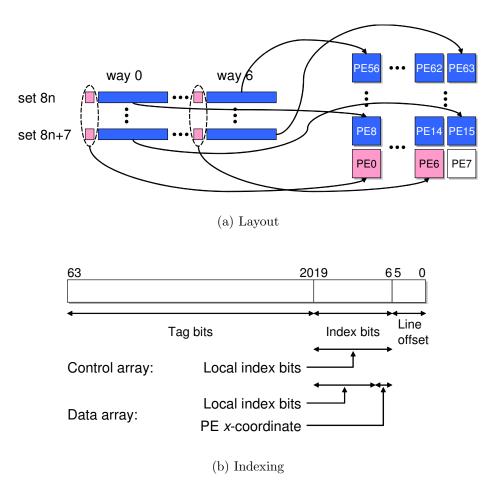

| 19 | Decoupled WLP cache (7-way 7MB cache)                                                                                             | 54 |

| 20 | Decoupled WBLP cache (7-way 7MB cache)                                                                                            | 55 |

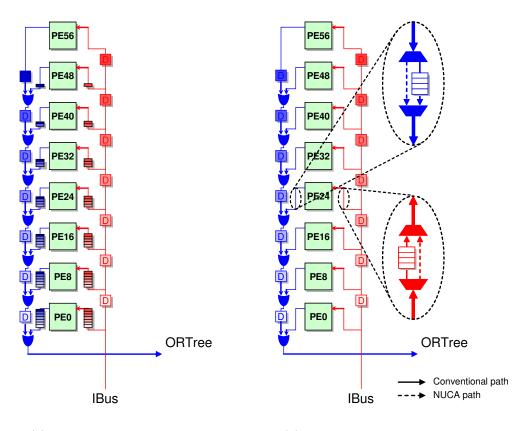

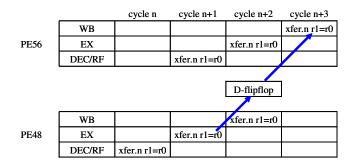

| 21 | Execution model (column 0 only)                                                                                                   | 57 |

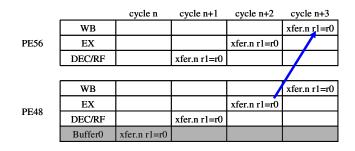

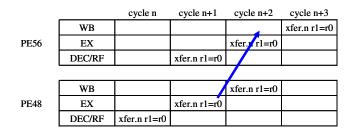

| 22 | Conventional and NUCA execution model of a xfer.n instruction                                                                     | 59 |

| 23 | Conventional and NUCA execution model of a xfer.s instruction                                                                     | 60 |

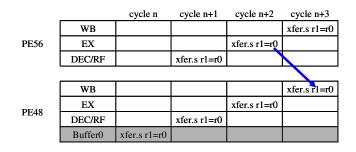

| 24 | LRU management of a NUCA C-mode (decoupled WLP cache)                                                                             | 62 |

| 25 | P-mode prefetcher.                                                                                                                | 65 |

| 26 | Hybrid design (cache + prefetcher). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                 | 67  |

|----|------------------------------------------------------------------------------------------------------------------|-----|

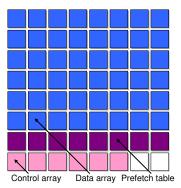

| 27 | AdaptiveCP-mode (MPKC: misses per kilo cycles).                                                                  | 69  |

| 28 | Relative performance of different C-mode designs                                                                 | 73  |

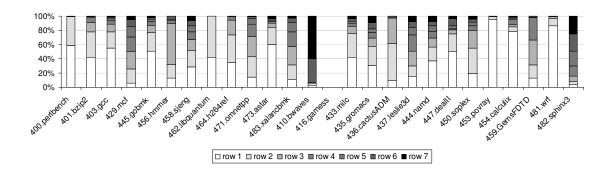

| 29 | Distribution of hit rows.                                                                                        | 74  |

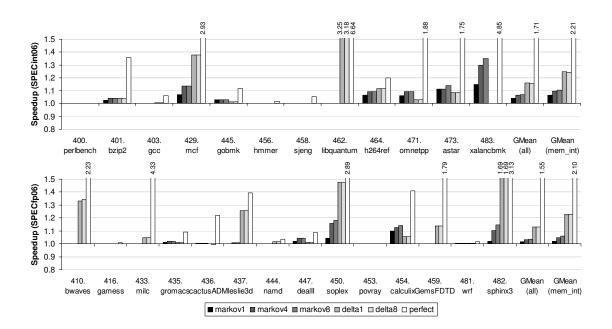

| 30 | Relative performance of different P-mode designs                                                                 | 76  |

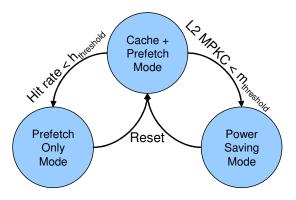

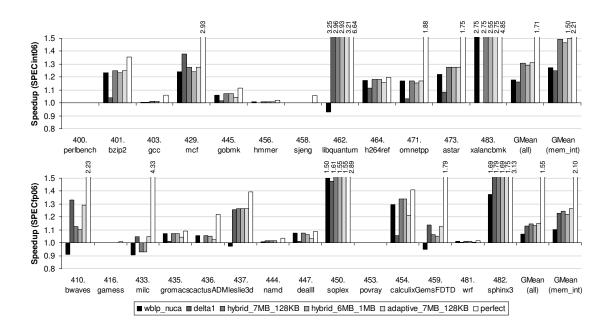

| 31 | Relative performance of Hybrid<br>CP-mode and Adaptive<br>CP-mode. $\ .$ .                                       | 77  |

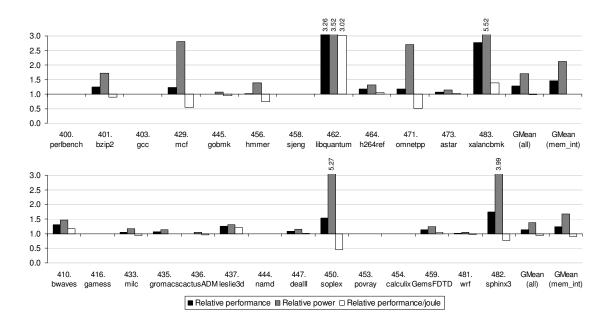

| 32 | Performance, power, and performance per joule of the AdaptiveCP-mode.                                            | 80  |

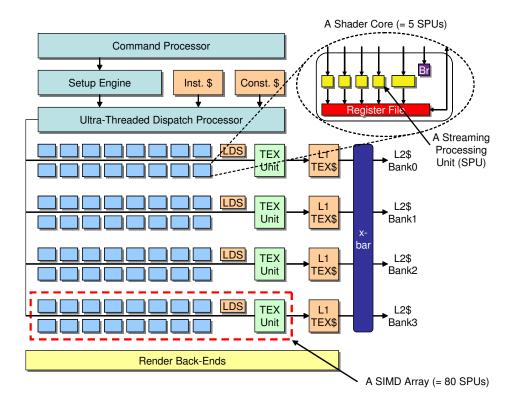

| 33 | Baseline GPU architecture                                                                                        | 85  |

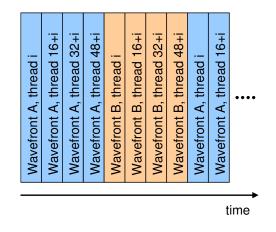

| 34 | Thread scheduling at SIMD core i of a 16-way SIMD engine                                                         | 87  |

| 35 | Integrated platform.                                                                                             | 88  |

| 36 | Miss address provider.                                                                                           | 90  |

| 37 | Hardware prefetcher vs. COMPASS                                                                                  | 92  |

| 38 | Stride prefetching.                                                                                              | 93  |

| 39 | Markov prefetching (prefetch width: 3)                                                                           | 98  |

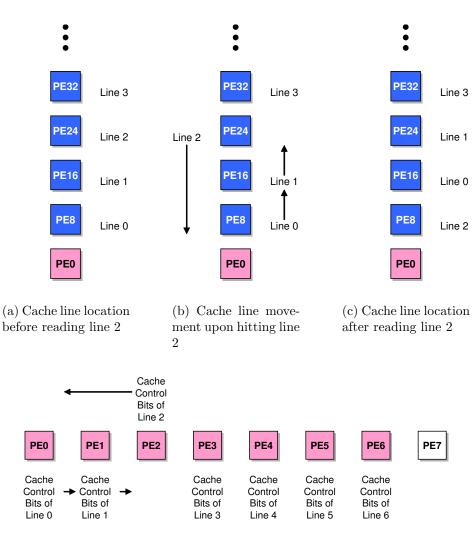

| 40 | Delta prefetching ( $\delta_i$ : $i^{th}$ entry of a delta buffer)                                               | 99  |

| 41 | Region prefetching                                                                                               | 101 |

| 42 | Exponential stride prefetching ( $\delta_0$ : a current stride, $\delta_1$ : the last stride).                   | 102 |

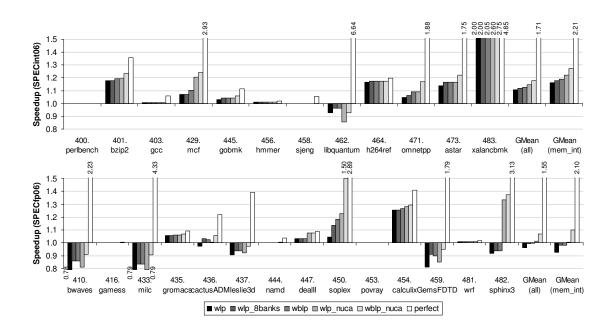

| 43 | Evaluation of Stride COMPASS (ST: single-threaded, MT: multi-threaded<br>ZI: zero-latency, infinite-throughput). |     |

| 44 | Evaluation of Markov COMPASS (ST: single-threaded, ZI: zero-latency, infinite-throughput).                       | 107 |

| 45 | Evaluation of Delta COMPASS (MT: multi-threaded, ZI: zero-latency, infinite-throughput).                         | 109 |

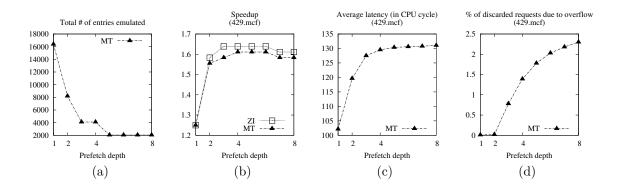

| 46 | Evaluation of custom COMPASS for 429.mcf (MT: multi-threaded, ZI: zero-latency, infinite-throughput).            | 110 |

#### SUMMARY

This thesis describes the efficient design of a future many-core processor that can provide higher performance under the limited chip power budget. To achieve such a goal, this thesis first develops an analytical framework within which computer architects can estimate achievable performance improvement of different many-core architectures given the same power budget. From this study, this thesis found that a future many-core processor needs (1) energy-efficient parallel cores and (2) a highperformance sequential core. Based on these observations, this thesis proposes an energy-efficient broad-purpose acceleration layer that can be snapped on top of a conventional general-purpose processor. In addition to such an energy-efficient parallel cores, this thesis also proposes different architectural techniques to further boost the performance of sequential computation while those parallel cores are idle. In particular, this thesis develops low-cost architectural techniques to enhance the memory performance of a host core by utilizing those idle parallel cores. This idea is evaluated in two different system architectures: one with the aforementioned acceleration layer and the other with an emerging integrated CPU and GPU chip.

# CHAPTER I

# INTRODUCTION

Unsustainable power consumption and ever-increasing design and verification complexity have driven the microprocessor industry to integrate multiple cores on a single die, called a multicore processor, as an architectural solution to sustaining Moore's Law [44]. With dual-core and quad-core processors on the market and an oct-core processor on the horizon, researchers are already a step ahead. They are investigating architectures, compilers, and programming models for a many-core processor with hundreds or even thousands of cores on a single platform [49, 57].

To integrate this number of cores on a single die, computer architects must address the problem of the fundamental physical limit, power consumption, to make a manycore architecture viable. For future many-core processors, low power will be not only a feature, but also a design constraint. In other words, achieving the goal of integrating a large number of cores onto one chip boils down to one issue, how to design many processing cores so that they do not consume more power than the chip power budget.

To address this question, we proposed an analytical framework within which computer architects can estimate achievable performance improvement of different manycore architectures given the same power budget [127]. This study provided us two interesting insights. The first insight is that building smaller, but more efficient parallel processors provides greater performance than replicating a state-of-the-art superscalar processor. The second insight is that sequential performance is not only important to improve overall performance, but also critical to achieve higher energy efficiency.

To achieve both energy efficiency and best-of-class single-thread performance, we also proposed a 3D-integrated broad-purpose acceleration layer that can be snapped on top of a conventional superscalar processor die [125]. Building such an efficient acceleration layer with a conventional superscalar processor poses several challenging problems. The first problem is binary compatibility between the host processor and the acceleration layer. Because the host superscalar processor is a complex instruction set computer (CISC) superscalar processor such as Intel Core and each parallel core in the acceleration layer is an energy-efficient, very long instruction word (VLIW) processor, the host processor should have an efficient mechanism to solve the problem of binary heterogeneity. The second problem is efficient interaction between the host processor and the parallel cores. As the host processor issues instructions in an out-of-order fashion by nature, either the parallel cores should be able to roll-back from misspeculation, or the host processor should be able to issue instructions in a different way. The third problem is designing an efficient interconnection network. As an interconnection network shares the same area and power budget with all other computation resources, the interconnection network should be as efficient as possible so that we can implement more computation resources instead. In this research, we designed the acceleration layer focusing on these three problems.

Although such an efficient asymmetric, heterogeneous many-core processor can provide high performance when running well-parallelized applications, such an architecture has a certain drawback: parallel cores are underutilized when the processor runs a single-thread application or the sequential code of a multi-thread application. During such a sequential computation phase, parallel cores of an asymmetric manycore processor remain idle while consuming area and power if not properly turned off. Instead of leaving them idle, we envision that we can utilize them to achieve higher single-thread performance by virtualizing them as a last-level cache and a data prefetcher. In the meantime, the overhead of such architectural techniques should be low enough that they do not compromise the efficiency of the baseline asymmetric many-core processor. Thus, in this research, we propose low-overhead architectural techniques that can virtualize these idle resources for higher single-thread performance and evaluate their hardware and power overheads [126].

In addition, we also design and evaluate such an idea in a CPU and GPU integrated platform, which many industry leaders plan to commercialize [128]. From this study, we found that we have lots of interesting challenges in such an integrated platform. For example, a conventional GPU does not have large cache or scratch pad memories. Furthermore, the GPU pipeline is optimized for throughput, not for latency, which makes our goal, reducing memory latency, even more challenging. In this study, we address these challenges by exploiting properties of a conventional GPU with negligible hardware overhead so that our new proposal does not harm the performance of conventional 3D graphics or general-purpose GPU applications.

The remainder of this document is organized as follows. Chapter II enumerates prior studies related with this thesis. Chapter III proposes an analytical framework within which computer architects can estimate the energy-efficiency of different manycore designs. Chapter IV proposes a 3D-integrated broad-purpose acceleration layer that provides a power-scalable parallel execution engine. Moreover, Chapter V proposes low-overhead architectural techniques to reuse such an accelerator, when it is idle, as a virtualized last-level cache or a virtualized data prefetcher. Chapter VI further extends the idea of reusing idle heterogeneous cores for boosting the singlethread performance of central processing units (CPUs) on the same die; It proposes architectural techniques to reuse idle graphics processing unit (GPU) cores for the same purposes. Chapter VII concludes this dissertation.

# CHAPTER II

# ORIGIN AND HISTORY OF THE PROBLEM

#### 2.1 Amdahl's Law

Amdahl's law [5] is used for predicting the maximum performance improvement when a new technique for improving the performance of a system applies to a subset of the system. A very good usage of it is parallel software. Parallel software programmers use Amdahl's law to estimate the theoretical maximum speedup of their parallelized software. Recent studies use Amdahl's law to estimate the performance of future many-core processors. Cho and Melhem extended the original Amdahl's law to find the optimal clock frequencies for serial and parallel code of a parallel program [24]. Hill and Marty proposed an extended Amdahl's law to show how much speedup can be achieved with different many-core processor designs given a fixed chip area [51].

#### 2.2 Massively Parallel Processors

While this research revisits the massive single-instruction, multiple-data (SIMD) concept of massively parallel processors (MPPs), this research expands and interprets the SIMD concept with modern requirements and technological constraints. The closest architectures are Maspar MP-1 [10, 82, 93] and Thinking Machines CM-2 [122]. Both of these machines centered the concept of a very large number of processing tiles for parallel calculations. This style of SIMD machine was broadly characterized as having a stand-alone front-end system that consists of a host processor. Both machines take advantage of the relatively free wire latency compared to the transistor switching speed and have a reasonable communication latency between nearest-neighbor processing elements (four cycles for CM-2 and eight cycles for Maspar). The nearestneighbor connections are supplemented with sophisticated networks, which allow allto-all, unstructured, and long-distance communication. The high number of processing elements (PEs) led to a sophisticated global network design with many layers of switches and crossbars. In the case of CM-2, it provided an *n*-way hypercube interconnect that linked clusters of PEs to other clusters. MP-1 utilized a multi-stage, multi-pass network that enabled arbitrary communications patterns albeit with substantially higher latency and setup costs.

Other important SIMD machines include Solomon [111], IBM GF-11 [69], and Illiac IV [13]. Some hybrid efforts between a multiple-instruction, multiple-data (MIMD) and a SIMD architecture were undertaken [115] but remain on the fringe. Systolic arrays [12, 70] resemble SIMD machines but were tailored for applications whose computations fit a narrower structure. In most cases, for higher efficiency, programmers need to map execution and data flow of an application in details to the target machine. Tarantula [33] extended Alpha instruction set architecture (ISA) with a slew of new instructions. EV8 understands an entire vector ISA for a renaming, a retirement, and a speculation issue and supports deep conditionals via masks. However, it does not support communication among vector units except for gather-scatter operations. VIRAM1 [38] is a vector processor with embedded dynamic random access memory (DRAM) for mobile multimedia devices.

Common SIMD use in modern processors is most evident in streaming SIMD extension (SSE) and 3DNow! extension as well as AltiVec or VMX Power Architecture extensions. These instructions were added to baseline ISAs to enable programmers and compilers to exploit data parallelism in media applications.

Imagine [4, 64, 106] is a stream-model processor but acts as a co-processor. Imagine uses a 128 KB stream register file to contain data while each attached arithmetic cluster has a local register file and several dedicated arithmetic logic units (ALUs) to operate on stream data in a producer-consumer model. Imagine capitalizes on an eight-wide SIMD ability inside each full ALU tile. The drawback is that each of the eight sub-ALU blocks is wired with a crossbar to full streaming register files, and applications must be ported to a stream-based model for exposing the parallelism.

#### 2.3 Tiled Architecture

Non-SIMD tile-based architectures, e.g., MIT RAW [117, 116] and UT-Austin TRIPS [108], have also been proposed. The RAW processor provides local instruction and data caches, contains 64KB of random access memory (RAM) in each processor tile for programming a dynamic and static router, and has its ALU bypass network tied directly into the interconnection network. To support its programming model, the RAW also has large memory space and additional modes dedicated to routing logic based on application needs for either static or dynamic routing. This approach requires extra logic and power compared to a pure SIMD design. TRIPS is tile-based, but it uses more sophisticated ISA mechanisms relying on a compiler analysis and static placement of computation. It also provides separate interconnection networks for data and instruction movement, and each tile has a complete CPU. The whole design is intended to support highly speculative parallelization techniques.

#### 2.4 Accelerator Architecture

IBM Cell Broadband Engine [52], an alternative to tile-based designs, hosts eight synergistic processor elements (SPEs) on a PowerPC host. These SPEs are complete with instruction fetch, decode, and branch control and work in a MIMD fashion. Each SPE also provides 256KB of static random access memory (SRAM) for local program and data. SPEs are connected to a planar ring network and perform direct memory access (DMA) operations to transfer information from and to memory.

Recently, a general-purpose graphics processing unit (GPGPU) [77] has been attracting more interest from the high-performance computing market. Tesla [95] is a GPGPU-based on a multi-threaded architecture for high-performance computing. It has 128 multi-threaded processors and supports up to 76.8 GBps of off-chip memory bandwidth but supports only IEEE 754 single-precision floating point operations. PhysX [3] is a specialized accelerator dedicated only to real-time physics to enrich game playing. ParallAX [129] was recently proposed as a future physics processor with detailed behavioral analysis of physics simulation.

### 2.5 Snap-On 3D Stacked Layers

In addition to its various advantages, 3D IC stacking technology also allows computer architects to snap on a new feature on top of a conventional product with reasonable cost. Mysore *et al.* proposed integrating specialized monitoring hardware stacked on top of the processor die using the 3D IC stacking technology [90]. On the other hand, Madan *et al.* proposed integrating a redundant checker processor on a second die to improve reliability of a processor [79].

#### 2.6 Software Caching

Many systems have used software caching techniques. To improve the programmability of synergetic processing elements (SPEs) on IBM Cell/BE, IBM provides a software cache library as a part of the IBM Cell software development kit [7, 32]. The MIT Raw processor used software caching to emulate both instruction [84] and data cache [86]. The Stanford VMP multiprocessor handled cache misses using software techniques [22]. Furthermore, prior studies developed advanced compiler techniques to better manage a software cache memory [123, 62, 20]. While the goal of all these prior studies is to improve the programmability or the performance of a processor with their local scratch-pad memory, our proposed design is to provide a virtualized last-level cache to a host processor to improve the single-thread performance of the host processor.

# 2.7 Shared Cache Management

To use on-chip memory resources more efficiently, researchers have focused on managing a shared cache [67, 130, 18, 47, 53, 102, 42]. Zhang and Asanovic proposed a new cache management policy called victim replication, which combines the advantages of private and shared schemes in a tiled CMP [130]. Chang and Sohi used private caches for both dynamic sharing and performance isolation [18]. Harris proposed a synergetic caching policy that groups neighboring cores into a cluster to have shared memory space among them [47]. While these prior studies attempt to manage shared cache more efficiently, our work addresses the underutilization issue of heterogeneous multicore processors by virtualizing unused PEs.

# 2.8 Non-Uniform Cache Architecture

To tackle the long latency problem of the last-level cache, researchers proposed a nonuniform cache architecture (NUCA). Kim *et al.* proposed an adaptive, non-uniform cache structure [65]. On the other hand, Huh *et al.* studied an optimal degree of cache sharing in a NUCA [56]. Unlike the original NUCA proposal, NuRAPID decouples the tag and data array to enable flexible data placement [23]. Although our research adopts the idea of a NUCA, we propose an architectural solution called *time-zoning* to provide non-uniform cache access latency on a SIMD engine with a strictly synchronized execution model.

# 2.9 Prefetching Techniques

Hardware prefetching is widely investigated by prior studies [19, 60, 92, 63, 92, 74, 26]. These hardware prefetchers use dedicated hardware blocks to predict and bring in the cache lines in advance whereas COMPASS is designed to reuse the existing GPU hardware and leverage their programmability and flexibility so that one (*e.g.*, software vendors) can write or select the most appropriate COMPASS shader to improve the

performance of their applications. On the other hand, software prefetching was also investigated by prior studies [16, 21], and various data prefetch instructions were added in almost every commercial microprocessor. These techniques basically insert software instructions into a code so that a future memory fetch can be initiated in advance. COMPASS is different from a conventional software prefetching technique because of the following. First, COMPASS does not consume any compute bandwidth of the main processor, rather, it leverages the idle GPU to perform the task. Second, it emulates a hardware prefetcher and its associated hardware (*e.g.*, prefetch table). As we demonstrated, the emulated table oftentimes is much larger than the practical size of a real hardware table. Third, COMPASS does not require re-compilation of a code.

Helper thread techniques [30, 25, 78, 6, 73, 89] were proposed to prefetch cache lines by precomputing load addresses. They often relied on another thread running on the same processor (*e.g.*, SMT or Multicore) to achieve their goal. As such, they could diminish the return if they compete the same resources needed by their master thread. Similar to software prefetching, these techniques usually run a stripped-down slice of the original program to precompute miss addresses and bring in those data in time. An event-driven helper thread [37] is proposed to emulate a hardware prefetcher on an idle CPU.

# CHAPTER III

# EXTENDING AMDAHL'S LAW FOR ENERGY-EFFICIENT COMPUTING IN THE MANY-CORE ERA

In 1967, Gene Amdahl proposed an often overlooked law of scaling: Sequential computation of a program largely limits the maximum achievable speedup [5]. This implies that any nonparallel execution or intercore communication will rapidly diminish the performance scalability for parallel applications regardless of the amount of additional computation resources. A simple, yet insightful, observation, Amdahl's law continues to serve as a guideline for parallel programmers to assess the upper bound of the attainable performance.

Unfortunately, beyond performance, computer architects face another grand challenge: energy efficiency. Architects should carefully design a future many-core processor so that its power consumption does not exceed its power budget [87]. For example, a 16-core processor with each core consuming an average of 20 watts will lead to 320 watts total power when all cores are active. This level of consumption can easily exceed a single-chip power budget. In other words, the amount of power that each core consumes will dictate the number of cores that architects can integrate on-die. Apparently, power is becoming more critical than performance in scaling up many-core processors. Thus, before integrating a large number of cores on-chip to provide desired performance and throughput, architects must maximize the power efficiency of each core.

Tackling these new design challenges requires extending Amdahl's law to account

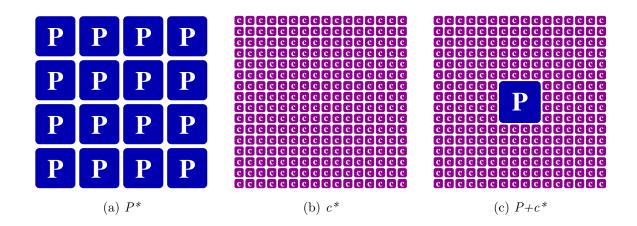

Figure 1: Many-core design styles.

for implications of power scalability in the coming many-core era. As the original Amdahl's law demonstrates, a simple analytical model can provide computer architects with useful insights. By using simple analytical models at the early design phase, architects can easily understand energy-efficiency limits, some feasible many-core design options, and future directions for making many-core processors more scalable.

# 3.1 Many-Core Design Styles

For this study, future many-core architectures are classified into three types. The first is a symmetric many-core processor that simply replicates a state-of-the-art superscalar processor on a die, as in Figure 1(a). High-end multicore processor vendors such as Intel and AMD use this approach. It is flexible and general enough to run different processes simultaneously while providing the best single-thread performance. Additionally, it can run independent threads spawned from one process to improve the performance of a single application. We use P to represent a single state-of-the-art superscalar processor and  $P^*$  to represent this type of many-core design style.

As Figure 1(b) shows, the second design style is a symmetric many-core processor that replicates a smaller, yet more power-efficient, core on a die. Embedded manycore processors, such as PicoChip [29], Connex Machine [43], and TILE64 [120], use this approach. The performance of a processing core using this approach is not as high as that of a state-of-the-art superscalar processor. However, architects can integrate more processing cores on a die using this approach; thus the aggregate onchip performance might be comparable to  $P^*$ . We use c to denote a smaller, more power-efficient processing core and  $c^*$  to represent this many-core design style.

The third design style, shown in Figure 1(c), is an asymmetric many-core processor that contains many efficient cores ( $c^*$ ) and one full-blown processor (P) as the host. The Sony-Toshiba-IBM (STI) Cell Broadband Engine [52] is an example of such a heterogeneous implementation. This design style lacks the flexibility to run different processes simultaneously. Nevertheless, the single-thread performance on the host processor should be high because it guarantees state-of-the-art sequential performance for certain applications. Moreover, it provides highly parallel performance when the efficient cores are in use. We use  $P+c^*$  to represent this design style.

#### 3.2 Augmenting Amdahl's Law

While Amdahl mainly focused on performance scalability back in the 1960s, we are more interested in the power scalability or energy efficiency of future many-core processors. Here, we develop analytical power models of each design and formulate metrics to evaluate energy efficiency on the basis of performance and power models.

#### **3.2.1** Models for $P^*$

According to Amdahl's law, the formula for computing the theoretical maximum speedup (or performance) achievable through parallelization is as follows:

$$Perf = \frac{1}{(1-f) + \frac{f}{n}},\tag{1}$$

where n is the number of processors, and f is the fraction of computation that programmers can parallelize  $(0 \le f \le 1)$ . To model the power consumption for a  $P^*$  many-core processor, we introduce a new variable, k, to represent the fraction of power the processor consumes in idle state  $(0 \le k \le 1)$ . We assume that one superscalar processor in active state consumes a power of 1. By definition, the amount of power one full-blown processor consumes during the sequential computation phase is 1, while the remaining (n-1) full-blown processors consume (n-1)k. Thus, during the sequential computation phase, P\* consumes 1 + (n-1)k. For the parallel computation phase, n full-blown processors consume n amount of power. Because it takes (1-f) and f/n to execute the sequential and parallel code, respectively, the formula for average power consumption (denoted by W) for a  $P^*$  is as follows:

$$W = \frac{(1-f) \times \{1 + (n-1)k\} + \frac{f}{n} \times n}{(1-f) + \frac{f}{n}}$$

$$= \frac{1 + (n-1)k(1-f)}{(1-f) + \frac{f}{n}}.$$

(2)

Now, we can model *performance per watt* (*Perf/W*), which represents the performance achievable at the same cooling capacity, based on the average power (W) in Equation (2). This metric is essentially the reciprocal of energy, because *performance* is defined as the reciprocal of execution time. Because *Perf/W* of single-core execution is 1, *Perf/W* benefit of a  $P^*$  is expressed as

$$Perf/W = \frac{1}{(1-f) + \frac{f}{n}} \times \frac{(1-f) + \frac{f}{n}}{1 + (n-1)k(1-f)}$$

$$= \frac{1}{1 + (n-1)k(1-f)}.$$

(3)

In addition to Perf/W, we can model *performance per joule (Perf/J)*, a metric to evaluate the performance achievable within the same battery life cycle or, more specifically, energy. Perf/J is equivalent to the reciprocal of *Energy-Delay Product* [40]. Using Equation (1) and Equation (3), *performance per joule* is as follows:

$$Perf/J = \frac{1}{(1-f) + \frac{f}{n}} \times \frac{1}{1 + (n-1)k(1-f)}.$$

#### **3.2.2** Models for $c^*$

The performance model of a  $c^*$  many-core processor has been a topic of Mark Hill and Michael Marty's recent research [51]. This model assumes that one larger core consumes the same amount of die area that several smaller cores consume. We slightly modified this performance model to accommodate arbitrarily sized cores. To model the performance difference between a full-blown processor (P) and an efficient core (c), we introduce a new variable,  $s_c$ . This variable represents the performance of an efficient core, normalized to that of a full-blown processor ( $0 \le s_c \le 1$ ). Since the performance of each efficient core is  $s_c$ , the formula for calculating the performance model of a  $c^*$  is as follows:

$$Perf = \frac{s_c}{(1-f) + \frac{f}{n}}.$$

To model the power consumption of a  $c^*$ , we need two new variables:  $w_c$  and  $k_c$ . The first variable represents the relative power consumption of an active efficient core to that of an active full-blown processor ( $0 \le w_c \le 1$ ); the second represents the fraction of idle power of an efficient core normalized to the overall power consumption of the same core ( $0 \le k_c \le 1$ ). During the sequential computation phase, one efficient core in active state consumes  $w_c$ , and all idle cores consume  $(n-1) \times w_c \times k_c$ . During the parallel computation phase, all efficient cores consume  $n \times w_c$ . Because it takes

$(1-f)/s_c$  and  $f/(n \times s_c)$  to perform sequential and parallel computation, respectively, the average power consumption by a  $c^*$  is

$$W = \frac{\frac{1-f}{s_c} \times \{w_c + (n-1)w_c k_c\} + \frac{f}{ns_c} \times nw_c}{\frac{1-f}{s_c} + \frac{f}{ns_c}}$$

$$= \frac{w_c + (n-1)w_c k_c (1-f)}{(1-f) + \frac{f}{n}}.$$

Thus, the following equations can represent Perf/W and Perf/J:

$$Perf/W = \frac{s_c}{w_c + (n-1)w_c k_c (1-f)}$$

and

$$Perf/J = \frac{s_c}{(1-f) + \frac{f}{n}} \times \frac{s_c}{w_c + (n-1)w_c k_c (1-f)}$$

#### **3.2.3** Models for $P+c^*$

Hill and Marty have also studied the performance model of a  $P+c^*$  many-core processor [51]. We slightly modify this performance model. Executing the sequential code at the host processor (one P) takes (1 - f), whereas executing the parallel code using the efficient cores takes  $f/(n-1)s_c$ . (A  $P+c^*$  many-core processor contains one P and (n-1) c cores.) Note that we assume the host processor to be idle while the efficient cores are executing the parallel code. Thus, the formula for computing performance improvement using a  $P+c^*$  is as follows:

$$Perf = \frac{1}{(1-f) + \frac{f}{(n-1)s_c}}.$$

During the sequential computation phase, the amount of power the full-blown processor consumes is 1, and the amount the efficient cores consumes is  $(n-1)w_ck_c$ . During the parallel computation phase, its full-blown processor consumes k, while the efficient cores consume  $(n-1)w_c$ . Because executing sequential and parallel code takes (1-f) and  $f/(n-1)s_c$ , the average power is

$$W = \frac{(1-f)\left\{1 + (n-1)w_c k_c\right\} + \frac{f}{s_c} \left\{\frac{k}{n-1} + w_c\right\}}{(1-f) + \frac{f}{(n-1)s_c}}.$$

(4)

Consequently, the Perf/W of a  $P+c^*$  is expressed as

Perf/W

$$= \frac{1}{(1-f)\left\{1+(n-1)w_ck_c\right\} + \frac{f}{s_c}\left\{\frac{k}{n-1} + w_c\right\}}$$

(5)

and the Perf/J of a  $P+c^*$  as

$$Perf/J = \frac{1}{(1-f) + \frac{f}{(n-1)s_c}} \times (6)$$

$$\frac{1}{(1-f) \{1 + (n-1)w_ck_c\} + \frac{f}{s_c} \left\{\frac{k}{n-1} + w_c\right\}}.$$

#### 3.2.4 Power-Equivalent Models

Because the limited power budget is one of the most critical design constraints, comparing different designs without considering the single-chip power budget is meaningless. Two main factors limit power growth on a single chip: power supply and power density. Power supply is proportional to the energy cost for sustaining machines in data centers as well as a concern for the battery life of portable devices. Power density pertains to the extra complexity and cost of thermal control mechanisms. From the power budget perspective, take, for example, a full-blown processor and an efficient core that consume 20 W and 5 W, respectively. Given a 160-W maximum power budget, we can integrate only eight full-blown processors or 32 efficient cores on a single die. Thus, to perform an apples-to-apples comparison for a given power budget envelope, we developed power-equivalent models by converting the number of cores of a  $c^*$  or  $P + c^*$  to an equivalent number of full-blown processors of a  $P^*$ .

Let  $W_{budget}$  be the single-chip power budget and  $n_{P^*}$  be the maximum number of full-blown processors we can implement on a  $P^*$  die. Because the amount of power consumption by a full-blown processor is modeled as 1,  $n_{P^*}$  full-blown processors on a die can consume up to  $n_{P^*}$ . Therefore, the maximum number of full-blown processors on a  $P^*$  is  $n_{P^*} = W_{budget}$ .

Conversely,  $n_{c^*}$  cores of a  $c^*$  consume power up to  $n_{c^*} \times w_c$ , which should be less than or equal to  $W_{budget}$ . So, the maximum number of efficient cores on a  $c^*$  is  $n_{c^*} = W_{budget}/w_c$ .

Similarly,  $n_{P+c^*}$  cores of a  $P+c^*$  consume power up to  $1 + (n_{P+c^*} - 1)w_c$ . Again, a single-chip power budget,  $W_{budget}$ , constrains the number of cores that an architect can implement on a chip. Consequently, the maximum  $n_{P+c^*}$  is

$$n_{P+c^*} = 1 + \frac{W_{budget} - 1}{w_c}.$$

Using these equations, we can uniformly represent and compare *performance*, Perf/W, and Perf/J of each many-core style with respect to a single-chip power budget.

#### 3.3 Evaluation

#### **3.3.1** Evaluation of a $P^*$

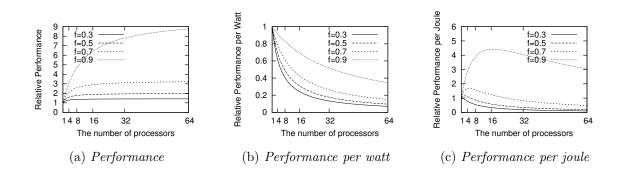

Figure 2(b) shows the Perf/W of a  $P^*$ . Unfortunately, parallel execution on a  $P^*$  consumes much more energy than sequential execution to complete the task. In the ideal case of f = 1, in which we can parallelize the entire code,  $P^*$  can achieve the maximum Perf/W— that is, 1. In other words, a sequential execution and its parallel execution version will consume the same amount of energy only when the performance improvement through parallelization scales linearly. Otherwise, a  $P^*$  must dissipate more energy to finish the same task. This occurs because performance does not scale linearly, as Figure 2(a) shows, but the amount of idle power does scale linearly with the number of cores.

Another interesting implication of this outcome addresses battery life. If one wants to optimize the system for a longer battery life, it is better to run several processes on different cores rather than parallelize each process and time-multiplex multitask them. Although the number of processes is less than the number of cores, spawning as few threads as possible so that different processes can run simultaneously is more power efficient. This improved efficiency is because Perf/W becomes worse as the number of cores increases. Furthermore, this result implies that maximizing and balancing parallelization among processors is also important, not only for higher performance but also for power-supply efficiency and extended battery life. However, no matter how well the code is parallelized or its performance scales, parallelization on a  $P^*$  many-core processor will always consume more energy unless the parallel performance scales perfectly linearly.

Figure 2(c) shows the Perf/J of a  $P^*$ . The evaluation result demonstrates that, if the performance of a parallelized application scales well, one can expect performance improvement at the same energy budget. In other words, a  $P^*$  can extract greater performance when running embarrassingly parallel applications given the same amount

Figure 2: Performance, performance per watt, and performance per joule of a  $P^*$  (k = 0.3).

of energy. For example, when f = 0.9 and k = 0.3, a 16-core  $P^*$  can achieve more than four times speedup than a single-core processor using the same amount of energy.

However, parallelization on a  $P^*$  does not always lead to better Perf/J, as Figure 2(c) shows. For example, an application, half of which we can parallelize (f = 0.5), loses energy efficiency if it runs on eight full-blown processors. This means that, from both the Perf/W and Perf/J perspectives, efforts to parallelize applications that can not be parallelized well might not be useful at all.

Another interesting observation is the existence of an optimal number of cores to achieve the best possible Perf/J. So, if one is particularly interested in tuning a system for this metric, dynamic monitoring and adaptively adjusting the system will be helpful. For example, given a 32-core  $P^*$ , it is wise to enable only 17 full-blown processors when running an application with f = 0.9 — that is, 90 percent of it can be parallelized. In this case, it is best to completely shut off the remaining 15 full-blown processors to suppress unnecessary idle energy consumption.

#### 3.3.2 Evaluation of a c\*

To evaluate the performance and power consumption of a  $c^*$ , we must model the relationship between the performance and the size of a core. To do this, we use Fred Pollack's performance efficiency rule [101]. It states that, given the same process

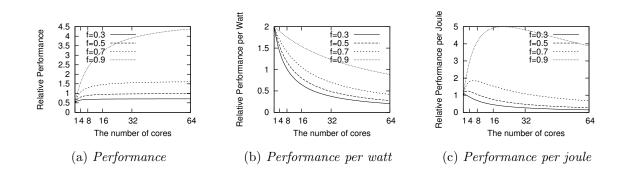

**Figure 3:** Performance, performance per watt, and performance per joule of a  $c^*$   $(s_c = 0.5, w_c = 0.25, \text{ and } k_c = 0.2).$

technology, the state-of-the-art processor provides 1.5 to 1.7 times higher performance and consumes 2 to 3 times the die area compared with its previous-generation counterpart. This means that a processor that consumes T times more transistors can provide only  $\sqrt{T}$  times higher performance. On the other hand, the rule also implies that the processor is  $\sqrt{T}$  times less efficient in terms of area. Another rule of thumb used in this evaluation is that the amount of power consumption of a core is proportional to the number of transistors it contains.

Figure 3 shows the analytical results of a  $c^*$ . In this analysis, we assume that each efficient core c has one-fourth the number of transistors of a full-blown processor P. We then model the amount of power consumption of this efficient core as one fourth of that of a full-blown processor ( $w_c = 0.25$ ). We also assume the performance of the efficient core as one half of that of a full-blown processor ( $s_c = 0.5$ ) and its fraction of power to be 20 percent ( $k_c = 0.2$ ).

Figure 3(a) shows that the maximum speedup of this  $c^*$  is not as high as that of  $P^*$ . The primary reason is that the sequential performance of an efficient core is lower. As Amdahl's law says, sequential performance strictly limits the maximum speedup, and a  $c^*$  design quickly levels off the speedup. Figure 3(b) shows that, when the number of cores is small, a  $c^*$  consumes less energy than a single-core, full-blown

**Figure 4:** Performance, performance per watt, and performance per joule of a  $P+c^*$   $(k = 0.3, s_c = 0.5, w_c = 0.25, \text{ and } k_c = 0.2).$

processor baseline. This occurs mainly because the performance-to-power ratio of an efficient core is better than that of a full-blown processor. Unfortunately, as the number of cores increases, the amount of energy consumption becomes higher than that of a single-core full-blown processor baseline. Furthermore, Figure 3(c) shows that the Perf/J of a  $c^*$  is not good either, unless the application is embarrassingly parallel — that is, it has high f values. This means that performance saturation is the major contributor that leads to a low Perf/J.

#### **3.3.3** Evaluation of a $P+c^*$

Figure 4(b) shows the Perf/W of a  $P+c^*$ , where  $s_c$ ,  $w_c$ , and  $k_c$  are modeled as 0.5, 0.25, and 0.2, respectively. Unlike a  $P^*$  or  $c^*$ , whose Perf/W monotonically decreases, an optimal number of cores exists that consume the least amount of energy to execute an application. For example, we can improve the Perf/W of an embarrassingly parallel application (f = 0.9) by about 50 percent when eight cores execute it.

However, Perf/W becomes worse than that of a one-core baseline processor when the number of cores exceeds a certain peak. There are two reasons for this result: relative power efficiency of efficient cores and performance saturation. When the number of cores is small, the additional performance benefit gained by adding one efficient core to the host processor dominates additional power overhead, so Perf/W

**Figure 5:** Power-equivalent models  $(k = 0.3, s_c = 0.5, w_c = 0.25, and k_c = 0.2)$ .

increases. However, once performance improvement starts to saturate, as Figure 4(a) shows, additional power overhead dominates. Thus, Perf/W decreases, as in Figure 4(b). In an energy-constrained environment such as embedded systems, how to spawn the optimal number of threads and turn off unused cores is an interesting topic of investigation.

Figure 4(c) shows the Perf/J of a  $P+c^*$ . Because of its low-latency sequential execution and energy-efficient parallel execution, a  $P+c^*$  achieves the best Perf/J compared with the two previous designs.

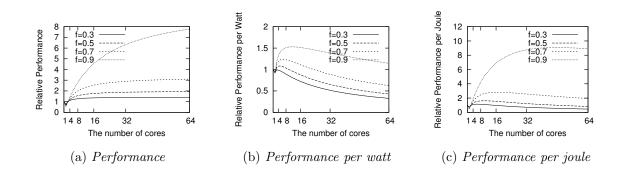

#### 3.3.4 Evaluation of Power-Equivalent Models

In addition to evaluating each many-core design style on its own, we use powerequivalent models to perform cross-design comparisons. Because the power budget is the major design constraint, the amount of power one core consumes determines the number of cores architects can implement on a single die. So, to compare different many-core designs, it is better to study performance and energy efficiency with the same power budget, rather than with the same number of cores.

Figure 5 shows the evaluation results with power-equivalent models. We assume each efficient core to consume one-fourth the power of a full-blown processor  $(w_c = 0.25)$  and its performance to be half that of a full-blown processor  $(s_c = 0.5)$ . As Figure 5(a) and Figure 5(d) show, the power-equivalent performance of a  $P+c^*$ is found to be highest in most cases. The power-equivalent performance of a  $P^*$  approaches that of a  $P+c^*$  when f is small. As f increases, the difference between them grows, because a  $P+c^*$  can have more cores at the same power budget. The powerequivalent performance of a  $c^*$  improves as f increases, as Figure 5(a) and Figure 5(d) show, but it is still the lowest among the three in most cases.

When f = 0.9 and the relative power budget is very low, the power-equivalent performance of a  $c^*$  is the highest (a pointer highlights this area in Figure 5(d)). In other words, in terms of performance itself, a  $c^*$  is preferable only when applications contain a huge amount of parallelism, and the system is extremely power-limited. Embedded devices designed for multimedia or data-streaming applications fall into this category.

Figure 5(b) and Figure 5(e) show power-equivalent Perf/W. When the relative chip power budget is small, a  $c^*$  consumes the least amount of energy to finish a task. However, when the budget is reasonably large, a  $P+c^*$  always consumes the least amount of energy. We explain these relationships as follows: When the power budget is small, a  $c^*$  can finish the task quickly owing to more processing power. As the power budget increases, this benefit diminishes because of the performance saturation resulting from its low sequential performance. This effect continues to degrade the  $c^*$  as the budget increases and eventually causes the Perf/W of a  $c^*$  to become even worse than that of a  $P^*$ . Similarly, Figure 5(c) and Figure 5(f) show that the Perf/J of a  $c^*$  is the highest only when the power budget is low and the task is embarrassingly parallel (f = 0.9). However, as the power budget increases, the Perf/J of a  $c^*$  many-core processor is worse than that of the other designs. Instead, a  $P+c^*$  is the most power-scalable. Thanks to its high sequential performance along with energy-efficient parallel computation capability, it achieved the highest Perf/J. To better understand the design spectrum, we also performed several sensitivity studies with different sizes of c and with different relationships between the performance and the power using these models. These studies showed similar trends.

# 3.4 Summary

Extending Amdahl's law to take power and energy into account, this study clearly demonstrates that a symmetric many-core processor can easily lose its energy efficiency as the number of cores increases. To achieve the best possible energy efficiency, this study suggests a many-core alternative featuring many small, energy-efficient cores integrated with a full-blown processor. This study also show that by knowing the amount of parallelism available in an application prior to execution, one can find the optimal number of active cores for maximizing performance for given cooling capacity and energy in a system. To further optimally control the number of active cores in an adaptive manner, a future many-core runtime needs to have the capability of dynamic per-core power profiling and a feedback mechanism to manage thread dispatch.

# CHAPTER IV

# A 3D-INTEGRATED BROAD-PURPOSE ACCELERATION LAYER

As shown in Chapter III, to provide high performance given a fixed power budget, computer architects should design a many-core processor that consists of a host processor designed for the highest single-thread performance and smaller but more cores designed for power-efficiency. One approach to achieve this goal is to incorporate ondie special-purpose accelerators with general-purpose cores. From an area-efficiency standpoint, however, it is impractical to specialize and accelerate all possible applications of interest. Furthermore, implementing several application-specific accelerators on a general-purpose platform has many drawbacks, such as longer design turnaround time, higher nonrecurring engineering cost, inflexibility, and lack of backward or forward binary compatibility.

To address these issues, this study proposes a broad-purpose accelerator design called parallel- on-demand (POD). Based on complex instruction set computer (CISC) superscalar processors (such as the Intel 64, formerly known as the Intel EM64T, processor), POD revisits several massively parallel single instruction, multiple data (SIMD) designs yet focuses on novel challenges including backward and forward binary compatibility, on-chip wire delay, and efficient interaction with a superscalar host processor. Furthermore, with emerging 3D die-stacking technology, a processor can flexibly snap a POD layer on top of a conventional general-purpose processor die with the ability of virtualizing different generations of a POD design. The snap-on feature of POD also lets processor vendors optionally upgrade a product during the packaging phase.

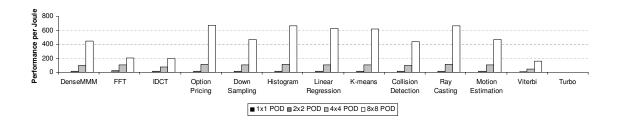

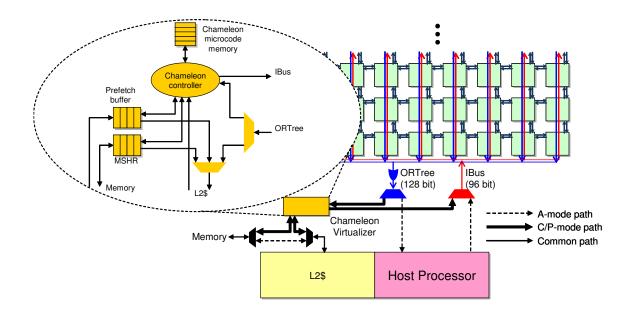

Figure 6: POD architecture in stacked die arrangement.

# 4.1 POD Architecture

Figure 6 is a high-level block diagram of the POD architecture, which consists of two die layers: a general-purpose processor (an Intel 64 processor) as the bottom layer and a snap-on accelerator, the POD layer. The general-purpose processor layer can be a die of a conventional multicore processor with design hooks. Depending on the target market segment, one can stack a POD layer on top at packaging time to improve performance per joule for certain applications such as high-definition multimedia, 3D games, or scientific computing. (The performance in performance per joule is defined as the inverse of execution time.)

During operation, the host Intel 64 processor fully boots a normal OS and runs every legacy application under that OS without deviating from current performance. At the instruction decode stage, the host processor might encounter a block of code written for POD to accelerate. In such a case, instructions within the block are broadcast to the POD layer through an instruction bus (IBus), of which each instruction

Figure 7: A processing element tile.

has the same fixed size. The processor might also broadcast 64-bit immediate values.

The POD layer is essentially a massively parallel SIMD processing element (PE) array. The target SIMD PE array is a sea of  $n \times n$  tiles, where n = 8 in Figure 6. The PE array executes instructions broadcast through the IBus and generates a flag-tree output that is tied together logically via an OR gate (ORTree) and is routed back to the host pipeline. The computed results from the PEs can be retrieved through the data return buffer (DRB) or memory hierarchy.

# 4.2 Heterogeneous ISA

Each PE tile contains a high-performance arithmetic unit with its own private register file and local SRAM memory (Figure 7). To provide a baseline performance level and support a subset of the host instruction set to facilitate PE virtualization, we use an existing 128-bit streaming SIMD extension (SSE) engine from a contemporary Intel 64 processor in POD. Although each PE will ideally be capable of decoding conventional CISC instructions for execution, this approach will require a large instruction decoder for each PE. This is less desirable when considering performance per square millimeter or performance per joule. Instead, to make each PE compact and efficient, we chose a very long instruction word (VLIW) execution model for the PE. The PE instructions, each 12 bytes wide, are broadcast from the host processor. Each 12-byte word forms a partially predecoded VLIW packet of three instructions that eliminate the CISC decoding overheads in POD. Each VLIW packet has a fixed format of one G (generic), one X (SSE), and one M (memory) pipeline instruction. Because the host processor orchestrates the execution of PE instructions, there is no need for implementing an instruction cache within the PE. Furthermore, because each PE is executing the same instruction and there is no instruction equivalent to a branch, no branch predictor or associated flush/control logic is required, which keeps the PE small and simple.

Because the host processor will orchestrate and broadcast POD instructions, we enhanced the Intel 64 instruction set architecture (ISA) to handle such heterogeneous instructions. To enable this, we added a new instruction prefix byte called *SendBits* to the existing Intel 64 ISA. When this prefix byte is encountered, it indicates that the following 12-byte word is an encapsulation of three POD operations. The host processor will then dispatch the 12-byte VLIW to the POD array. Also, we rely on the compiler or assembler to schedule and pack the three-way VLIW instructions.

Unlike conventional massive SIMD machines, the POD integrates a massive SIMD PE array with a modern out-of-order host processor. To ensure execution correctness, we should address two major challenges in the host processor: recovery from misspeculation and out-of-order dispatch of POD instructions. To support speculative execution, we need some recovery mechanism to roll the machine back to the correct architectural state. For example, Tarantula, which had relatively narrow SIMD engines attached to a superscalar processor, implemented a recovery mechanism in

Figure 8: IBits queue in the superscalar pipeline.

each PE [33]. Unfortunately, this results in substantial overhead to both the area and power for a massively parallel SIMD engine. To simplify the PE design (and build as many PEs as possible), we design the host processor of POD to broadcast POD instructions in a non-speculative manner. In other words, the POD instructions will not be dispatched from the host processor until its preceding branches are resolved. From a performance standpoint, as long as the code that runs on the host processor does not depend on the results from the POD, this approach will not degrade performance <sup>1</sup>.

Another issue is that the host processor might reorder the POD instructions, which might lead to incorrectness because the PE is ignorant of program order. To prevent such reordering, we strongly order the POD instructions by implementing an IBits queue along with a conventional out-of-order pipeline (Figure 8), similar to the store queue found in an out-of-order processor. When a SendBits instruction is issued, its 12-byte immediate field (encoding a VLIW POD instruction) is entered into the IBits queue. Upon the retirement of the SendBits instruction from the reorder buffer (ROB), the corresponding 12-byte immediate value is latched onto the IBus and is

<sup>&</sup>lt;sup>1</sup>This is the case for all of benchmark programs that we evaluated in this study, except k-means. The host processor does not issue any data-dependent instruction that reads data updated by the POD immediately for these benchmark programs. This event is extremely rare even in k-means simulation.

broadcast to PEs.

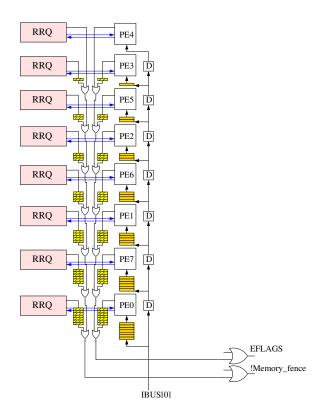

# 4.3 Wire-Delay-Aware Design

To enable SIMD-style instruction execution where every PE executes each instruction at the same global clock cycle, we have two design candidates: executing an instruction immediately upon arrival to a POD row, leading to a north-south time-zone effect, or buffering each arriving instruction for sufficient time such that every PE will execute the same instruction at the same instant.

The time-zone effect can be challenging for programmers and architects to work around, as any given row will be executing instruction j while the preceding row is executing j+1 and the successor row is executing j-1. To avoid undesired complexity for programmers, architects, and compilers, we use a buffering model to eliminate the time-zone effect and enable lock-step execution.

Figure 9 shows such a model for a single column in the POD. Instructions are broadcast using the IBus and queued before being executed by the PE. For n rows, it takes n-1 cycles before every PE executes the instruction. The queue size shrinks monotonically as the location of a PE gets farther away from the host processor<sup>2</sup>. For an  $n \times n$  POD, where n = 8, there are seven entries for the bottom-most PE while no queue is needed for the topmost PE. The delay units (D block) are inserted to delay each instruction broadcast to synchronize the SIMD execution. Similarly, when gathering results (such as EFLAGS) from PEs, the results from the PEs closer to the host processor must be delayed and wait in their queue until the farther results arrive for combining. Figure 9 depicts such queuing in the propagation paths with correct delay queues on the left side. Compared to the previous immediate execution model, there is no overhead to the PEs with this implementation except for a buffer to hold the instructions broadcast. The round-trip latency for the host processor to evaluate

<sup>&</sup>lt;sup>2</sup>Although each PE is identical, programmable fuses are burned after die manufacture to set the used numbers of slots in the queue.

Figure 9: One detailed POD column.

the conditional loop also remains the same, which, for n rows, is  $2 \times (n + f_0) + l$  cycles where 2n cycles are consumed for instruction and EFLAGS propagation,  $2f_0$  is fan-in and fanout latency between the host processor and PEs in the first row, and l is the actual instruction latency.

Regardless of how the PEs are connected to each other, the instruction and datavalue broadcast from the host processor are arranged as a fan-out tree. The bottommost row of the PE array will receive the same instruction at the same cycle. The instruction is then passed up to the next row in sequence. This fan-out tree is implemented on a POD layer so that the number of die-to-die vias between a generalpurpose processor layer and a POD layer remains unchanged (Figure 6), regardless of the number of PEs. This constant interface lets us extend a POD layer without redesigning a general-purpose layer every time we introduce a new product.

## 4.4 Energy-Efficient Interconnection Network

Figure 6 also shows that POD adopts a folded torus network [27]. To minimize latency and maximize packing, we designed each PE to be small enough so that signal propagation time over one PE is less than one clock cycle. Ideally, each side of a PE will be no longer in any direction than 95 percent of the wire distance in one clock cycle with all surrounding line drivers, buffers, and so forth. The ordering of the number labels inside the PEs of the leftmost column in Figure 9 indicates the northsouth nearest neighbor connection pattern. In the same way, the communication links for each row are laid out in east-west direction. In addition to providing shorter links, such a layout also leads to deterministic communication latency. The significance of such deterministic latency is that we can disable communication-related logic and wires safely when they are not used. Moreover, the lock-step execution model will make the entire computation predictable and fully debuggable. There are no tricky issues such as race condition, live lock, deadlock, and so on found in normal SMP-style many-core processors.

At any given moment, only one direction (input and output) must be enabled. Because each nearest-neighbor communication pattern has a known latency, and because the communication is directed by communication instructions, the links are disabled during the course of pure computation or when links in the other direction are not being used. Furthermore, no power-hungry routers are required for this pointto-point network. All we need are a single 4:1 multiplexer and a 1:4 demultiplexer for input and output, respectively. This reduced power profile allows growth of the POD array to be limited by the average power consumption of each PE and the manufacturing die reticle. This approach contrasts with other tiled designs such as the Raw processor from MIT [117] or the TRIPS processor from the University of Texas [108] where any of the interconnection network links could be active at the same time due to dynamic routing. Each PE can communicate with its nearest neighbor by either directly moving a register value of up to 128 bits or by transferring memory in 64-bit chunks. Because the nearest-neighbor latency for a folded torus is targeted to be two cycles or less, this allows for high-throughput computation even when the algorithm requires neighboring registers and memory values. A fully synchronized computation model allows register transfer operations to utilize full communication bandwidth without any network overhead, such as additional latency due to contention and header encoding overhead. In the case of memory transfer operations, only a half communication bandwidth can be utilized because the upper 64 bits are used to encode other information such as memory addresses.

When one PE needs to communicate to another PE in a non-nearest-neighbor fashion, we use the k-permutation routing in our interconnect design [41]. Rather than providing dynamic-wormhole-routing hardware support for a relatively infrequent operation, we use a dedicated algorithm to drive the collective POD multiplexers into a series of sweeps to migrate all data to the intended targets. These algorithms require each PE to support n hardware buffer slots (permutation queue) of the bit size matching the point-to-point link width in an  $n \times n$  SIMD array.